Other Parts Discussed in Thread: ADS8588S

Dear Technical Support Team,

I'd like to use the ADS8588SEVM as a stand-alone board without PHI board.

Q1-1

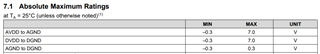

Is it possible to supply 2.5V to the 50-pin DVDD of the J9 connector from FPGA board?

Since the IO on the connected FPGA board side is 2.5V, I would like to use the Digital Output on the ADS8588S side as LVCMOS2.5V.

DC specifications of ADS8588S says that range of DVDD shows from 2.3V (min) to AVDD, so 2.5V seems to be no problem.

But if it is not intended to be used as LVCMOS 2.5V, is it better to avoid it?

Q1-2

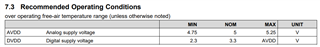

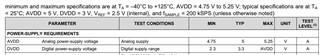

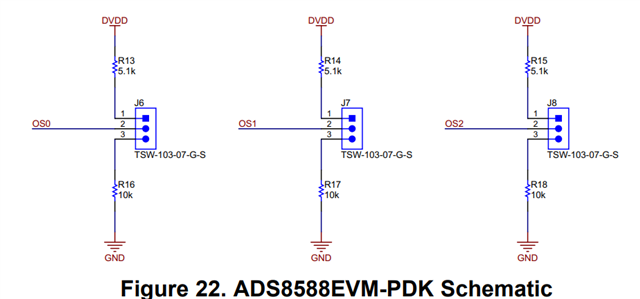

I'd like to know if other restrictions(Such as pullup/GND for STBYn / REFSEL / PARn_SER / RANGE / OS0/1/2 ) on ADS8588SEVM with DVDD=2.5V.

Q2

If it can be used with DVDD=2.5V, are the following VOL/VOH specifications of Digital IO correct?

VIH = 1.75V~2.8V

VIL = -0.3V~0.75V

VOH = 2.0V~2.5V

VOL = 0V~0.5V

Q3

Is it okay if pins 56, 58, and 59 of the J9 connector are floating?

I think the EEPROM contains information to inform the PHI board that the ADS8588S is installed on ADS8588SEVM , but I will not use PHI and use FPGA board.

Q4

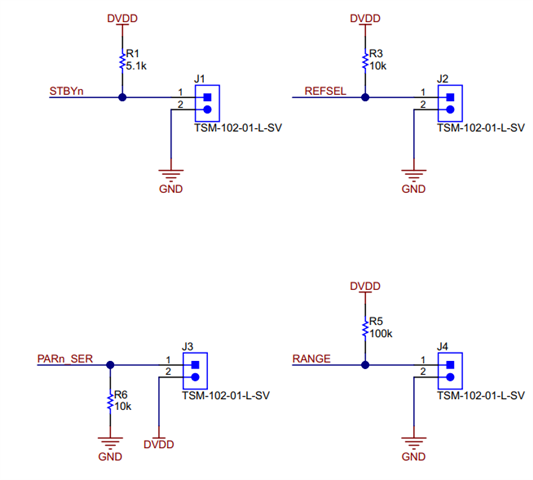

Datasheet "10 Power Supply Recommendations" shows following and it seems no sequencing between AVDD and DVDD.

----

There are no specific requirements with regard to the power-supply sequencing of the device. However, issue a reset after the supplies are powered and are stable to ensure the device is properly configured.

----

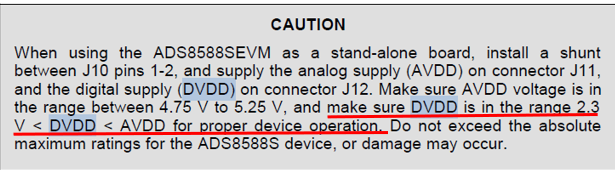

ADS8588EVM-PDK shows following.

Dose Red lined "make sure DVDD is in the range 2.3 V < DVDD < AVDD for proper device operation. " mean sequencing (First AVDD and Second DVDD) or no sequencing(Just a Voltage level)?

In my case, DVDD=2.5V are from FPGA through J9.

Is it OK in either order, DVDD => AVDD or AVDD => DVDD, and after the power supply is stable, is it proper device operation to set the initial ADC settings from FPGA after reset?

Best Regards,

ttd