- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello. I am currently testing a design using your ADC08100 converter. The ADC data is processed by an FPGA, that takes sums 24576 consecutive windows of 3072 samples.

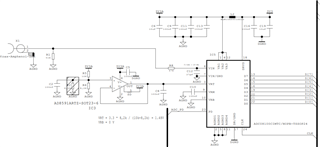

I am, however, experiencing an unusual noise on the data, and would like to understand why. The schematic is the following.

As said before, we have a program that takes 3072 samples from the ADC and stores it in memory. It does 24576 accumulating the data.

The ladder reference voltages are set up from 1.48V to 0V.

The ADC was connected through a short 50-ohm coaxial cable to a waveform generator and properly terminated. Here are some of the results.

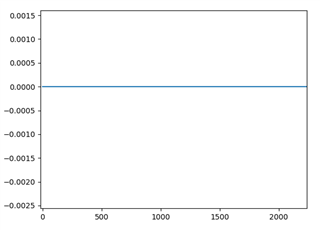

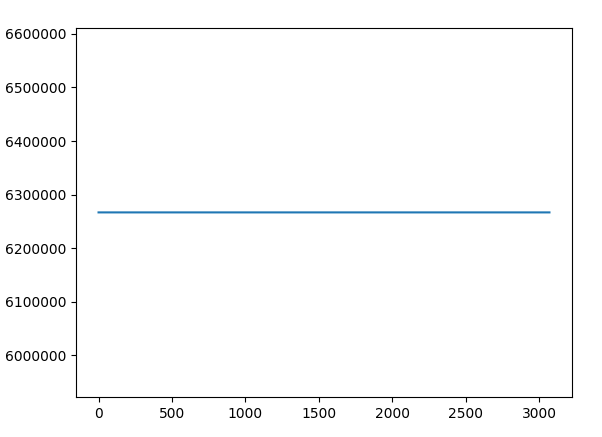

Stable when input is 0V.

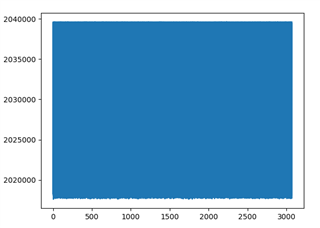

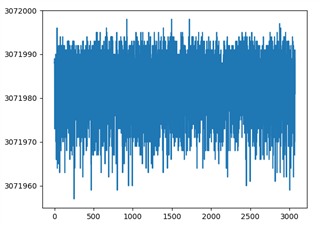

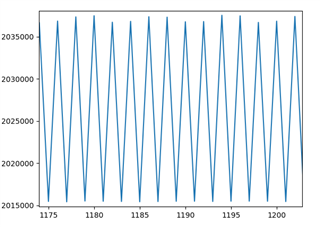

High synchronous noise when input is 0.5 V

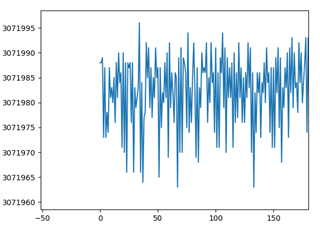

A more random looking noise when input is 0.75 V. This is what I would expect for all tests. The amplitude of the noise is much lower too.

Stable when input is 1.5 V.

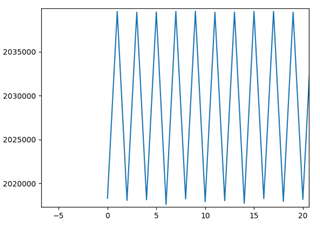

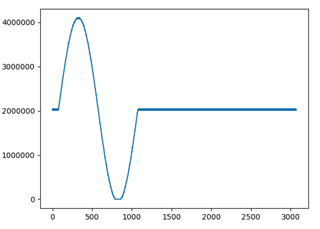

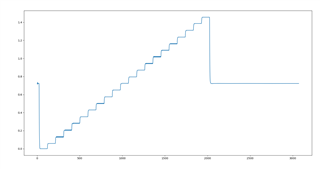

One period (0-1V) 100 kHz sine wave, triggered by a pin on the FPGA, synchronously (but with a delay) with the beggining of the sampling window. High synchronous noise when signal is DC.

Could this be an issue with my implementation of the ADC08100, or could it be an issue in the processing system? I think that the FPGA is executing correctly because the results are repeatable and seem correct.

NOTE: The issue still happens when the clock frequency is decreased to 50 MHz

Hi Ricardo,

Let me set up an EVM in our lab check this for you.

I will get back to in the next a few days.

Thanks,

Amy

Hello,

I set this up on our lab EVM and did not have issues getting a data capture.

Ensure that you have a solid connection between the CMOS outputs and your capture solution.

Additionally, probe the CLK line and ensure that the ADC is properly receiving the CLK signal.

Thanks,

Amy

The CMOS outputs are connected to the FPGA, with length matched traces and a very small length.

I probed the clock line and everything seems ok. The strange thing is this issue doesn't happen for some voltages, and it happens for smaller frequencies too (I tried down to 25 MHz). I will see if I can discover anything else useful.

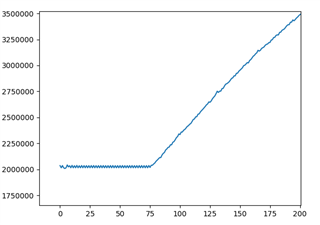

I tried to sweep some DC voltages across the ADC, and got the following result:

It is very obvious that the noise level on some voltages is not the same, and it doesn't seem to follow any type of pattern.

Hi Ricardo,

I noticed this was moved to an email thread.

I am going to close this post and continue things over email.

Thanks, Amy