Other Parts Discussed in Thread: TSW14J57EVM, LMK04828, LMX2592, , LMH6401, LMH5401, LMX2582

Hi,

We has some problems that our board doesn't communicate with TWS14J57EVM using HSDC Pro.

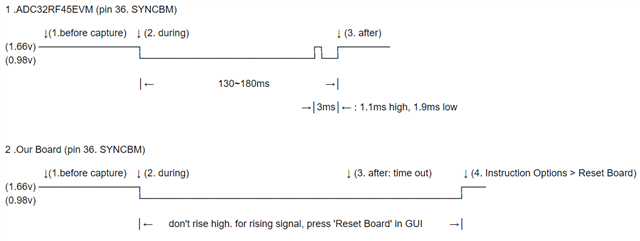

When I clicked the capture button,I observed a timeout message. The SYNC signal goes low and doesn't rise again.

Executing the "reset board" command in the GUI restores the SYNC signal to a high state.

However, a timeout consistently occurs when clicking the capture button.

We made a custom board based on ADC32RF45EVM to measure high speed photo detector's signal.

Since we don't have an FPGA development environments and are currently using the TSW14J57EVM as is, we've decided to proceed with creating the custom board separately.

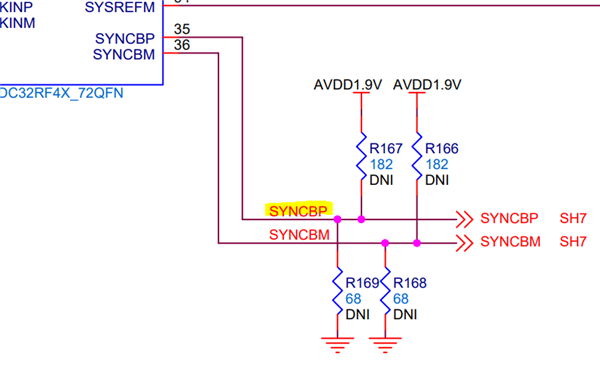

Our board included a micro controller(STM32F103) to Initialize ADC32RF45, LMK04828 and LMX2592 using SPI, and embedded LMH6401, LMH5401 for signal conditioning.

The wiring lengths for connections between chips or connect(FMC) changed by ADC32RF45EVM during the PCB board design.

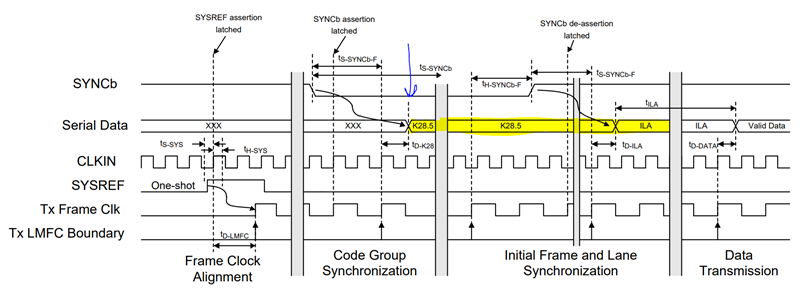

I made efforts to equalize the lengths of the differential lines, considering the sensitivity of the JESD204B standard to timing issues.

We checked the clocks going to each chip since communication wasn't established. I confirmed that the clock frequencies match those of the ADC32RF45EVM.

However, due to the limited bandwidth of the our oscilloscope, precise measurement of signal timing between them was not possible.

We are currently suspecting the clock timing and data lane timing between boards.

In particular, we suspect that the shortened length of the data lanes compared to the reference EVM board may be causing issues.

We are curious whether this suspicion is valid and if there are other aspects we should investigate.

Your advice would be greatly appreciated.

Thank you.