Other Parts Discussed in Thread: ADC128S102

Hello,

I got a ADC128S102EVM board and I am trying to communicate with the ADC using a ProAsic3e from Microsemi.

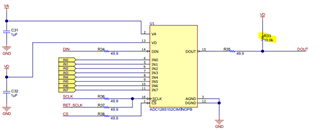

For this, I removed the resistor R42 to use an external VA/VREF (3.3V in my case) and I added a wire to supply VD with ProAsic3e 3.3V. The PHI board is not plugged, I am currently not using it to communicate with the ADC. The SPI communication comes from the ProAsic3e and is connected on J26.

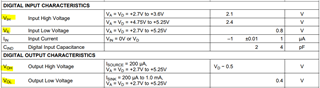

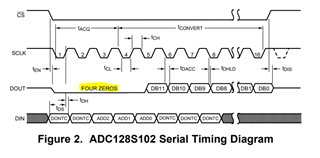

My problem is that I receive on DOUT the values of the ADC channel 0 regardless of the address (between b'000' and b'111') I try to send on DIN. However, if I send logicals 1 on DIN while CS is low, I got the value of the ADC channel 7. But it not the case if I send only b'111'.

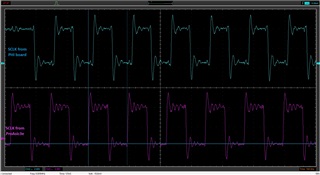

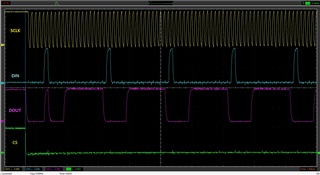

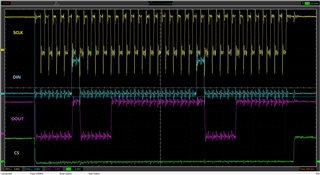

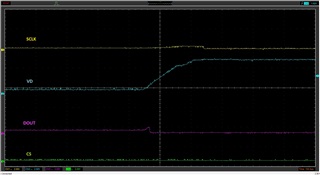

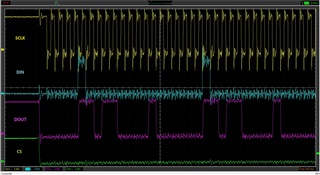

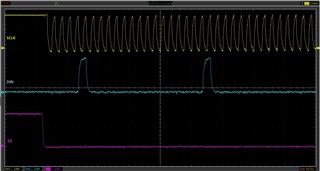

It looks like a timing problem but I have checked the control signals with an oscilloscope and they are following the protocol described on the ADC128S102 datasheet.

Here is what I send with the FPGA for reading the channel 1 of the ADC. (My probs are placed on J26)

I have checked that VA>=VD and it is the case.

I have first tested the ADC128S102EVM with the PHI board and the ADC128S102EVM GUI. In this case I can read every ADC channels without any problems. So the ADC128S102EVM is functioning correctly.

Any ideas of where there could be the problem?