Hello team,

Can ADC32RF55 used with M =1 for JESD204B?

Best Regards,

Kei Kuwahara

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello team,

Can ADC32RF55 used with M =1 for JESD204B?

Best Regards,

Kei Kuwahara

Kei-san,

You can configure the FPGA to only look at a single channel, but the ADC will need to be programmed into a dual channel mode. Since the fpga is the receiver and programmed for single converter, it will look for CGS/ILAS on just the single channel’s lane(s).

Regards, Chase

Hi Chase-san,

I have additional question.

The customer can program the FPGA to look for single channel lane, but can we operate ADC32RF55 with just 1ch lane of JESD204B?

The customer wants to reduce the lane rate of JESD204B.

Best Regards,

Kei Kuwahara

Hi Kei-san,

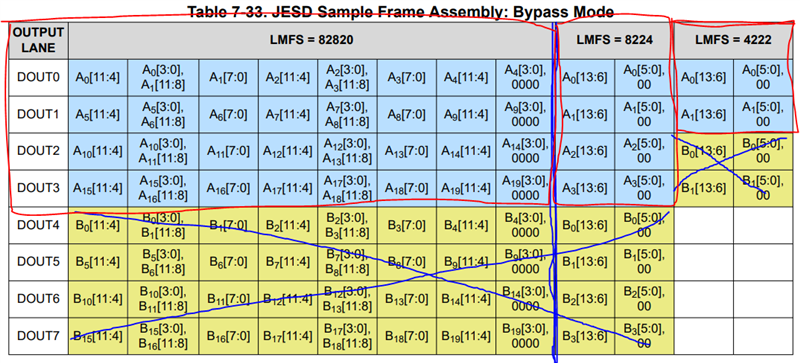

I am not sure I follow. If we just ignore all of the channel B jesd lanes and only consider channel A lanes, still, if the number of serdes lanes decreases then the datarate will typically increase if the resolution remains the same. Let's just consider how ignoring channel B would act for bypass modes. For bypass mode, the ADC has these options for frame format:

If we ignore all channel B data (yellow), then these new frame formats would change into (left to right):

The number of lanes (L) is reduced as well as the number of converters (M). The number of octets in a frame (F) and number of samples per converter per frame (S) will stay the same.

This device does not have a one register setting to powerdown channel A or B, however the customer can powerdown unused lanes to save power.

Thanks, Chase

Hi Chase-san,

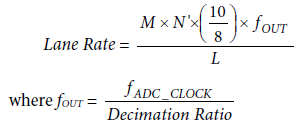

The customer wants to 1/2 just the M, to reduce the Lane Rate.

In this case, both M and L is 1/2, so the Lane Rate is still same.

I guess there is no way to reduce only the M for ADC32RF55. Is this correct?

Best Regards,

Kei Kuwahara

Hi Kei-san,

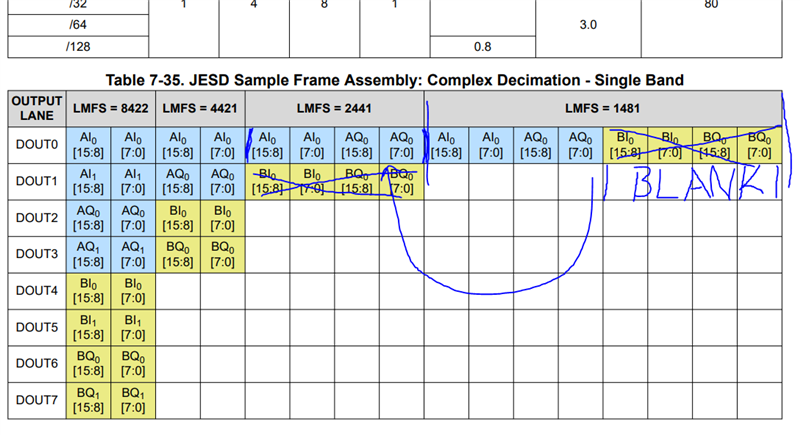

The most efficient data packing is already present because there are always modes present where the data is not interleaved.. See below.

If we consider the customer wanting to use 1-4-8-1 and then eliminate the second channel to half the M, the result would be half of the frame being empty. So instead, they could use 2-4-4-1 and then only take lane 1 to get the high efficient data for channel A alone.

Thanks, Chase

Hi Chase-san,

Thank you for the explaination.

In fact, the customer wants to reduce the data rate of the JESD204B because their FPGA can only take 12.5Gbps, and ADC32RF55 will output 12Gbps@3GSPS. (There is too little margin)

The customer knows that reducing the sampling rate of the ADC will reduce the output data rate, but they are looking for another way.

Is there any way to reduce the output data rate for JESD204B at 3GSPS sampling rate?

Best Regards,

Kei Kuwahara

Hi Kei-san,

Not in bypass mode. Only by reducing sample rate or by decimating.

Chase

Hi Chase-san,

Thank you for a very quick reply!

Understood completely.

You can close this thread.

Best Regards,

Kei Kuwahara