Hello, I'm having some issue initializing the DAC37J82 device.

What I'm trying to do is set up two JESD lanes on the SERDES lane0 & lane1 (RX0 and RX1) inputs, assign them to JESD lanes 0 and 1 in a single link0, pass them through the A & B data paths, and send them out the IOUTA and IOUTD pins. The input to the DACCLK pins is running at 250 MHz, and the JESD is intended to run at 2.5 Gbps, LMF=222.

I seem to be getting odd disparity issues after configuration and no data coming out of the DAC. Strangely enough, when I try the /K28.5/ test, it seems to pass in the device.

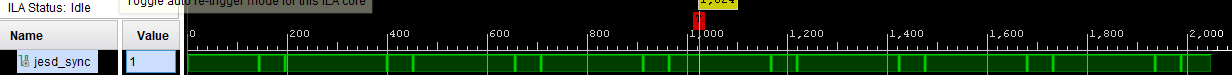

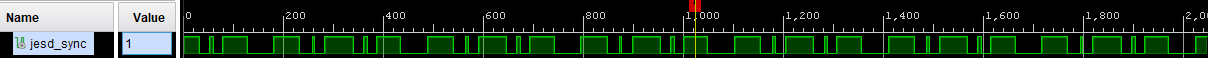

Standard operation: SYNC occasionally goes low in a repeated pattern, but stays high most of the time. 0x64 and 0x64 status registers read back 0x100 (8b/10b disparity error)

/K.28.5/ test mode: Stable SYNC (always high), 0x64 and 0x64 read back 0x0000 (no errors).

/D.21.5/ test mode: No SYNC, 0x64 and 0x65 status registers read back 0x400 (code synchronization error)

Repeating ILA test mode: SYNC occasionally goes low in a repeated pattern, but stays high most of the time, similar to standard operation. 0x64 and 0x64 read back 0x0000 (no errors).

If it helps, here's the initialization sequence I'm sending to the DAC:

1. Reset DAC pin via pin

2. Program DAC registers with these values:

Reg | Value { 0x23, 0x01ff }{ 0x1A, 0x0026 }{ 0x31, 0x1800 }{ 0x32, 0x0000 }{ 0x33, 0x0000 }{ 0x3D, 0x0088 }{ 0x3E, 0x0148 }{ 0x3B, 0x0000 }{ 0x3F, 0x0000 }{ 0x46, 0x0044 }{ 0x47, 0x190a }{ 0x48, 0x31c3 }{ 0x49, 0xFFF0 }{ 0x4A, 0x0320 }{ 0x5F, 0x0123 }{ 0x60, 0x4567 }{ 0x24, 0x0000 }{ 0x25, 0x2000 }{ 0x00, 0x211A }{ 0x03, 0xf300 }{ 0x4A, 0x033e }{ 0x4B, 0x1f01 }{ 0x4C, 0x1f01 }{ 0x4D, 0x0100 }{ 0x4E, 0x0f0f }{ 0x4F, 0x1C61 }{ 0x50, 0x0000 }{ 0x51, 0x00DC }{ 0x52, 0x00FF }{ 0x53, 0x0000 }{ 0x54, 0x00FC }{ 0x55, 0x00FF }{ 0x5C, 0x0008 }{ 0x5C, 0x0000 }{ 0x61, 0x0211 }{ 0x22, 0x101C }{ 0x02, 0x2002 }{ 0x04, 0xFCFC }{ 0x05, 0xEFF7 }{ 0x06, 0xFFFC }{ 0x14, 0x0000 }{ 0x15, 0x0000 }{ 0x16, 0x8000 }{ 0x0C, 0x01B0 }{ 0x0D, 0x0000 }{ 0x0E, 0x0000 }{ 0x0f, 0x0000 }{ 0x1E, 0x9999 }{ 0x1F, 0x8882 }{ 0x1F, 0x8880 }{ 0x20, 0x8008 }{ 0x26, 0x0000 }{ 0x2D, 0x0001 }{ 0x3C, 0x0050 }{ 0x64, 0x0000 }{ 0x65, 0x0000 }{ 0x66, 0x0000 }{ 0x67, 0x0000 }{ 0x68, 0x0000 }{ 0x69, 0x0000 }{ 0x6A, 0x0000 }{ 0x6B, 0x0000 }{ 0x6C, 0x0000 }{ 0x4A, 0x0321 }

3. Enable DAC TX via pin

4. Enable JESD TX from master device