Other Parts Discussed in Thread: AFE881H1, , AFE882H1

Hi Joseph,

we are facing problem with HART data transmission. I've given detailed description below.

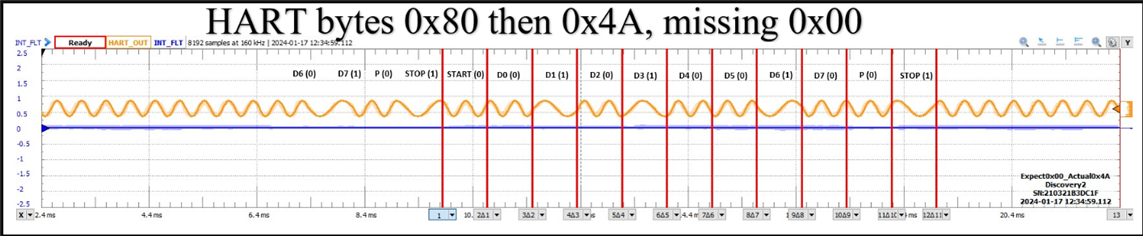

Problem: Approximately every hundred HART frames, one byte shortly after the preamble bytes is not transmitted on `HART_OUT`, despite being sent to AFE881H1 `FIFO_U2H_WR` register via SPI.

See the example SPI protocol trace, below. It shows 5 preamble bytes and then 11 data data bytes written to `FIFO_U2H_WR`.

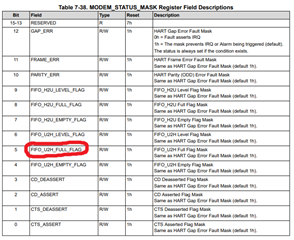

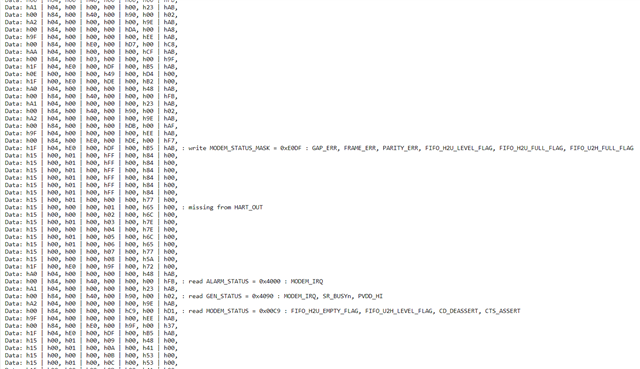

Data: h0E | h00, h00 | h00, h49 | h00, hD4 | h00, - assert RTS Data: hA0 | h04, h00 | h00, h00 | h00, h48 | hAB, - read ALARM_STATUS Data: h00 | h84, h00 | h40, h00 | h00, h00 | hFB, Data: hA1 | h04, h00 | h00, h00 | h00, h23 | hAB, - read GEN_STATUS Data: h00 | h84, h00 | h40, h00 | h90, h00 | h02, Data: hA2 | h04, h00 | h00, h00 | h00, h9E | hAB, - read MODEM_STATUS Data: h00 | h84, h00 | h00, h00 | hDB, h00 | hAF, Data: hA2 | h04, h00 | h00, h00 | h00, h9E | hAB, - read MODEM_STATUS Data: h00 | h84, h00 | h00, h00 | hD9, h00 | hA1, Data: h9F | h04, h00 | h00, h00 | h00, hEE | hAB, - read MODEM_STATUS_MASK Data: h00 | h84, h00 | hFC, h00 | hFA, h00 | hA0, Data: h1F | h04, hFC | h00, hF9 | h00, hEC | hAB, - write MODEM_STATUS_MASK Data: h15 | h00, h01 | h00, hFF | h00, h84 | h00, - write FIFO_U2H_WR Data: h15 | h00, h01 | h00, hFF | h00, h84 | h00, Data: h15 | h00, h01 | h00, hFF | h00, h84 | h00, Data: h15 | h00, h01 | h00, hFF | h00, h84 | h00, Data: h15 | h00, h01 | h00, hFF | h00, h84 | h00, Data: h15 | h00, h01 | h00, h00 | h00, h77 | h00, Data: h15 | h00, h00 | h00, h80 | h00, hEB | h00, Data: h15 | h00, h01 | h00, h00 | h00, h77 | h00, - not transmitted on HART_OUT Data: h15 | h00, h00 | h00, h4A | h00, h93 | h00, Data: h15 | h00, h01 | h00, h00 | h00, h77 | h00, Data: h15 | h00, h01 | h00, h0C | h00, h53 | h00, Data: h15 | h00, h00 | h00, hFE | h00, h96 | h00, Data: h15 | h00, h00 | h00, h8F | h00, hC6 | h00, Data: h15 | h00, h01 | h00, h71 | h00, h27 | h00, Data: h15 | h00, h01 | h00, h05 | h00, h6C | h00, Data: h15 | h00, h00 | h00, h07 | h00, h77 | h00,

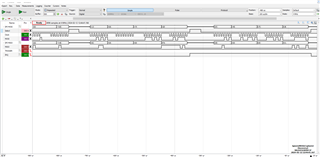

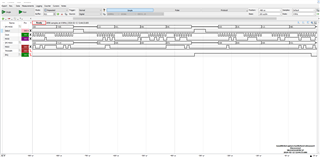

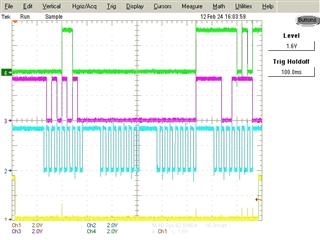

In this example, the third byte after the preamble bytes, value "0x00", is not transmitted on HART_OUT, despite being written to the U2H FIFO. The waveform below was captured with probe connected to TP15 on AFE881H1EVM.

The implementation follows the recommendation from the AFE881H1 datasheet, "7.3.5.9 HART Communication Using the SPI".

Assert the RTS. After CTS_ASSERT is set, begin to fill FIFO_U2H. Enqueue enough data into FIFO_U2H to fill the FIFO above the set threshold level.

This is noteworthy because the error does not occur (after tens of thousands of HART characters) when the data is written to U2H FIFO before asserting RTS.

Below are some error conditions that are eliminated as possible causes.

- `CRC_ERR` not set

- `FIFO_H2U_FULL_FLAG` IRQ enabled and never occurs

- Neither `GAP_ERR`, `FRAME_ERR`, nor `PARITY_ERR` bits set within `MODEM_STATUS` register.

The hardware setup consists of a two microcontroller boards and two AFE881H1EVM boards. The `HART_OUT` screw terminal of each AFE881H1EVM is connected to other's AFE881H1EVM `HART_IN` screw terminal. One microcontroller acts as a HART host, and the other acts as a HART device, waiting for a command. An Analog Discovery 2 is connected to the device-side AFE881H1EVM.

Some more system information below:

- AFE881H1 configured for SPI-only mode

- SCLK frequency 1 MHz

- RTS input pin always driven high

My initial question is, why might this issue only occur when RTS is asserted prior to writing data to U2H FIFO?

Regards

Asha G