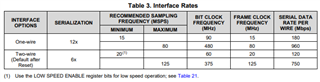

Could you tell me about ADC3424 LVDS DCLK frequency?

It is fixed value? Or it is changed dynamically by analog input value?

Now, I wonder DCLK frequency is changing each our product operation.

Sometimes, it is about 370MHz, but it is about 190MHz.

(I don't change ADC register between this trying.)

Is this phenomenon reasonable?

Could you tell me how is LVDS DCLK frequency determined?

Thank you.

Yoshinori Kikui