Part Number: TI-JESD204-IP

Hello,

Toolchain: VIVADO 2022.2

IP Core example: based on ZCU102 (with GTH)

Target Technology: Kintex Ultrascale KU035

During porting the design the following issues appeared:

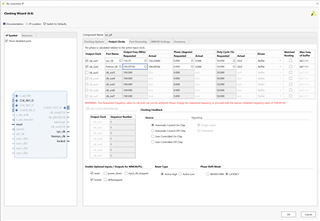

1. Xilinx Transceiver IP wizard needed to be upgraded from rev6 to rev14

2. PLL Could not generate exactly 100MHz so, changed to 100.09766MHz. DRP clock also set on the same frequency

3. Created a timer to generate the synchronous resets instead of VIO, triggered from QPLL0 lock, and activated at around 4.5uS

4. Set the cfg_rx_buffer_release_delay to 10 (arbitrary)

PLL Warning for 100MHz Clock:

I am testing the JESD204c IP core. I created a VHDL wrapper and a VHDL testbed to exercise the IP.

Testbed:

1. Connected cc_sysref_out to sysref

2. GTH ADC to DAC GTH

3. Sysclk = 156.25MHz

4. Refclk = 156.25MHz

5. adc_rx_sync connected to dax_tx_out

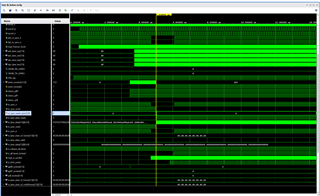

I see GTH activity prior de-asserting the Tx Sync Reset, but values are fixed (0xFF00 pattern)

Tx seems to start normally at approx. 4.5uS (see cursor on above screenshot).

Rx shows that lanes are locked at about 6uS.

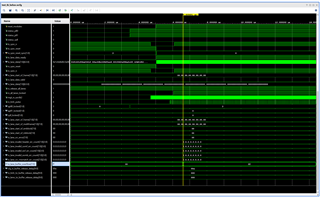

Rx_lane_data_valid is never active and I see overflow error after a while, as per below screenshot.

Can you help me to determine why the receiver is not getting any data?

Thanks,

Ilias