Hello guys,

One of my customers uses ADS8568 for their current mass-production.

Recently, the following phenomenon was observed on a specific ADS8568.

They have the questions as the follows.

Could you please give me your reply?

[Phenomenon]

At a specific ADS8568, when the board is turned off and then turned on again, the AD converter value becomes abnormal.

The AD converter itself is working, but the data conversion value is approximately 60% of the expected value.

It looks like the ADC internal reference setting (internal DAC output?) is abnormal, or the ADC internal conversion gain is abnormal.

This phenomenon is reproducible. If the power to the board turned off and turn it on again with AVDD (5V) remaining at 0.5V or more, the same phenomenon will occur with this same device.

If I wait until AVDD is below 0.5V, it works fine.

[ADS8568 setting]

1. /HW/SW terminal = L

2. /PAR/SER terminal = H

3. RANGE terminal = H

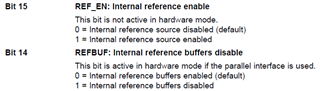

4. REFEN terminal = H

VREF is internal reference (2.5V)

[Questions]

1. Is there a possibility that this phenomenon will occur? Or is this device broken?

2. They initialized the device with RESET terminal H/L after this phenomenon was happened. But the abnormal phenomenon was not disappeared.

Which part of the function is reset by this reset pin ->L->H->L?

3. Does ADS8568 have any gain control block? If the answer is yes, can the gain control block be reset by RESET terminal L/H/L?

Your reply would be much appreciated.

Best regards,

Kazuya