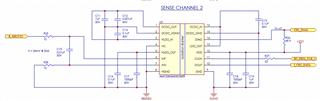

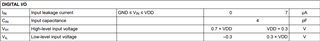

We are using an AMC3306M05 modulator on a recent board. We have noticed that occasionally, the device would not power up correctly with DCDC_OUT at ~1.8V and diagnostic pin low. After experimenting with the device, we found that if we disabled the clock (being driven from a microcontroller), the device would come up correctly. We also found that if we enabled and disabled the clock, it would fall back into this failure mode. We have three of these on the board, and all three behaved exactly the same -- that is, if one failed, all failed. So the root cause must be systematic.

We dug through the datasheet, and didn't find anything particular about gating the clock and restrictions around that (other than the amount of time before the output is stable). If I am operating and reprogram the microcontroller, the modulator sometimes lands in this failed state.

Any thought as to why this is happening? What restrictions are there on the clock?

I have seen the other post about the DCDC_OUT being ~1.8V, which sounds like a similar failure, but apparently different issue. Our clock frequency is 12MHz, but during power up/programming I guess it is possible to see a higher frequency for a period.

Thanks!