- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi all,

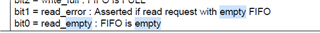

I am trying to configure the DAC38J84 in a custom board. I have the DAC PLL locked and the PLL serdes locked but I am getting the FIFO empty error no matter what I try.

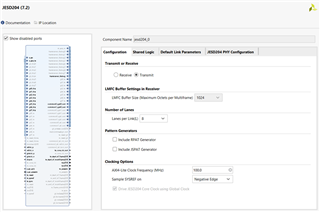

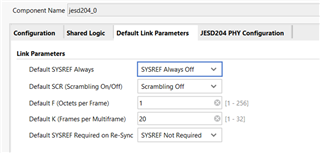

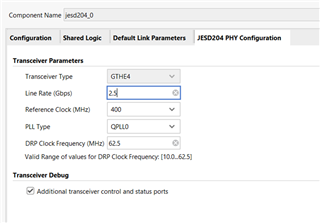

This is my configuration of the JESD IP core:

To sum up:

Parameters like K, F are the same in the JESD IP core and in the DAC.

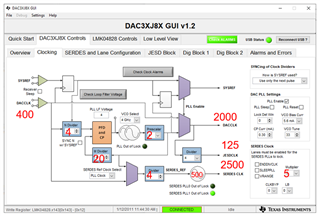

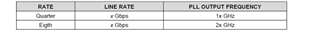

I configure the DAC PLL as in the next figure (I am not using the tool to configure the DAC as I am working with a custom board, but I use the image to explain my configuration).

After configuring the DAC, I can see the tx_ready signal at high level coming from the JESD IP core. Also the signal tx_start_of_multiframe is toggling so I assume the JESD IP core is sending data from the FPGA (we are using a Zynq Ulstrascale+).

My questions are:

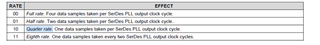

But I would like to understand this table also, how is defined “one data sample” in this table?

Having said all this, why I have the FIFO empty error in all the 8 lines?

Thank you so much in advance.

Hi Juan,

This device is subclass 1 only. It needs a sysref to align internal dividers for the jesd link. If there is no sysref present then this could cause the empty fifo issues. Do you have the ability to supply a sysref signal?

Thanks, Chase

Hi Chase,

Thanks for your response. We can generate a sysref periodic signal from our PLL.

So, even if you configure the DAC to not use sysref signal it is necessary to provide it with one?

Which is the relation that the frequency of the sysref must fulfill to work properly?

I just notice that when I set initial state to 0000 and release the jesd reset (0x4A -> 0xFF01) I get 0x03 in the alarm register for all lines (read_error and read_empty)

Also, the SYNCB pin is set to 0 at this moment.

I change my K from 20 to 2 to be able to generate a sysref clock from my PLL, now it is running at 25MHz.

LMFC = linerate/10/K/F = 2500/10/2/1 = 125MHz

sysref = LMFC/n = 125/5 = 25MHz

is it problematic to have sysref present before configuring the DAC?

Thanks!

Juan.

Hi again,

I have another question related to SYSREF, I am providing a SYSREF signal to my FPGA JESD core and other to my DAC38J84 chip generated from my PLL. I generated these two signals as normal outputs of the PLL so the SYSREF is always running from the first moment I configure this PLL in charge of generate of the main clocks of the design. Is there any problem in working this way? I know that having active SYSREF may cause some degradation in the spectrum of the generated signals but could it cause not to get the link up? (SYNCB signal is not going high again...).

PD: the SYSREF frequency is now 5MHz which I assume it fullfils the requirement of being linerate/10/K/n/F (K=2, F=1).

Thanks,

Juan.

Hi Juan,

If you have K set as 2, it may not allow adequate RBD for the link to come up correctly. Is it possible for you to set K as 16 and modify sysref accordingly?

Thanks, Chase