Other Parts Discussed in Thread: LMK04828

Hi Jim,

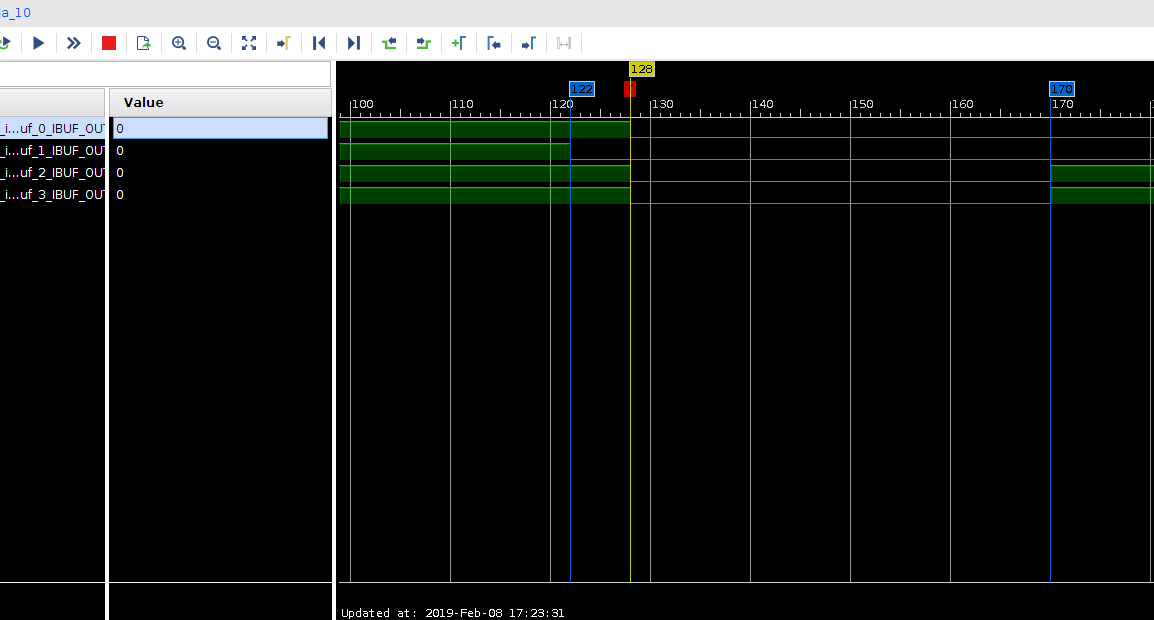

I have four DAC38J84s clocked by an LMK04828 and an FPGA (the ZCU102) attempting to establish JESD204B link between all four of them.

LMFS = 2441

Line Rate = 9.8304 Gbps

Sampling Frequency = 245.76 MHz with One-Shot Sysref (triggered via the SYNC request pin on the LMK).

Strangely enough, I'm able to establish a link and transmit on 2 of my four DACs. All DACs have the same config, and the LMK04828 has the same register values for the clocks going to each DAC.

For the two DACs that don't establish link, I'll get FIFO Alarms on the two active lanes after clearing and reading the following registers:

Lane 2 (0x66) = 0x3 or 0xb or 0x703

Lane 4 (0x67) = 0x3 or 0xb

I know these mean a SERDES FIFO Read or Write errors, but what kind should we change to address these? We don't think its our configs since they are all the same. I've attached them below. We have two separate files since we are using our own tool to program our DACs and LMK (and we've verified that our SPI reads and writes work).