Other Parts Discussed in Thread: SN74AUP1G125, , LMX1204, LMK04828

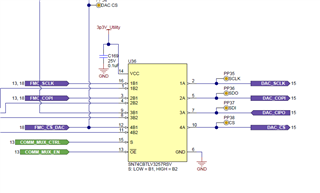

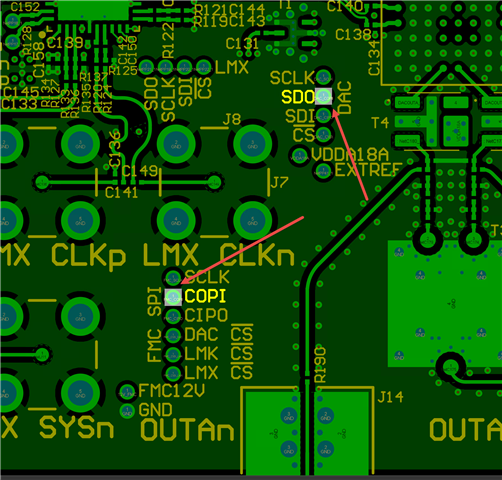

I noticed in the user manual that the ability to use SPI signals from the FMC+ connector will be supported on the next rev of the board. Is there a workaround for the current rev of the board to use the SPI signals from the FMC+ connector?