Other Parts Discussed in Thread: ADC32RF45

Hi Sir :

I used ADC32RF45 EVM and FPGA sent SYNC to ADC . but I measured ADC'output data which didn't show K-code(28.5).

Do you have any idea? this problem have been taken me lots of time.

thank you.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Sir :

I used ADC32RF45 EVM and FPGA sent SYNC to ADC . but I measured ADC'output data which didn't show K-code(28.5).

Do you have any idea? this problem have been taken me lots of time.

thank you.

Hi Chase :

Are you measuring SYNCb signal on ADC pin? -> yes

Is the correct pin mapped for SYNCb signal? -> yes

Are you using differential or cmos SYNCb? -> differential

Is this matching on both the FOGA and the ADC? -> yes , matching FPGA pin

Hi CIOU,

SYNCb is nominally high anytime the converter is not resyncing. This should remain high until the FPGA drives this pin low. When the pin is driven low by the FPGA we are in the CGS phase and the ADC will begin to output K28.5 symbols. After the FPGA receives enough of these symbols, it should release SYNCb back to logic high and the ADC will stop transmitting K28.5 symbols and instead output the sampled data. If the SYNCb signal never toggles low, then the device will never enter CGS phase. If the SYNCb goes low and does not come high again, the FPGA is unable to establish a link. Some common issues for this is incorrect lane configuration between the ADC and the FPGA. K value may not be correct on both FPGA and ADC. The K value may not be large enough to account for the lane timing skew across lanes. The lane mapping or lane polarity may be incorrect as well.

If the ADC is not sending the characters, try placing LINK LAYER TESTMODE register into 011 = Repeat the initial lane alignment (generates a K28.5 character and repeats lane alignment sequences continuously). This will allow you to examine the raw ADC data in the FPGA to see if all lanes are outputting K28.5 correctly.

Thanks, Chase

Hi Chase :

Following picture 1 , I made link layer test mode switch to K28.5 mode , and FPGA can receive K-code from ADC . following picture 2 .

But I changed test mode to normal ADC , FPGA can't receive K-code . even I triggered data = BCBCBCBC , FPGA didn't receive k-code. following picture 3 , 4.

by the way, you mentioned k value , in this condition k=16?

picture 1 :

picture 2 :

picture 3 :

picture 4 :

Hi CIOU,

The test pattern has confirmed the serdes interface looks ok for now, the problem must be that the SYNCb is not toggling correctly. Can you review this again and probe the lines (R168, R169).

Alternatively, the device supports cmos 1.8v sync using the GPIO4 pin (pin 63). The EVM has this connected onto the GPIO2 test point (TP7). These component values are all assuming RevD hardware. Can you confirm you have this version? If not, I can send you the appropriate version and suggest new values for probing and cmos sync test point.

The K value and elastic buffer size is important for the ILAS stage of the link bringup. We are still trying to get you past CGS phase right now so we can ignore the K value for now.

Thanks, Chase

Hi CIOU,

Please probe the GPIO2 test point (TP7) and share the oscilloscope capture. Please trigger the oscilloscope when you the FPGA drives SYNCb low. If you set the horizontal timescale wide, you can manually trigger the oscilloscope for one time capture and then assert SYNCb with the FPGA.

Thanks, Chase

Hi CIOU,

The ADC should be outputting K28.5 characters nonstop right now. If you force trigger the ILA right now, then you will see random data, such as 000000001234567? The data width is 64 bit but only 32 bit of data and is getting through. When in repeating ILA sequence, only 32 bit of bcbcbcbc are getting through.

I suggest to review that the clocks are correct for your transceiver configuration and that the transceiver configuration itself is correct. Unfortunately I cannot offer any further help on this since this is not using the TI-204C-IP and it seems to be FPGA related.

Thanks, Chase

Hi Chase :

I reviewed the clock of transceiver and transceiver configuration .

ADC GUI setting value , ADC sampling clock : 1.536Gsps , LMFS : 82820 , and serdes rate is 6.144Gbps. picture 1 .

FPGA JESD204 transceiver clock is 153.6MHz.

SO should I need to write any registers of ADC ?

thank you.

picture 1 :

There should be no ADC register writes needed. The JESD RX (ie FPGA) controls the link initialization. Is the FPGA pll locking? I am not able to offer much more help on this. The ADC config should be fine when you press PROGRAM EVM button. The only thing that may change would be the FPGA reference clock divider. If this is not correct the FPGA transceiver PLL may not be locking.

Hi Chase :

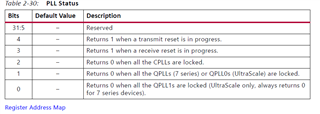

I confirmed the FPGA clock status, like picture 1 and picture 2 , jesd204 IP use CPLL. so the JESD204's register bit2 is 0 which means clock locked.

I don't know why ADC can't output K28.5.

Does anyone be able to help this?

thanks.

picture 1 :

picture 2 :