Hello,

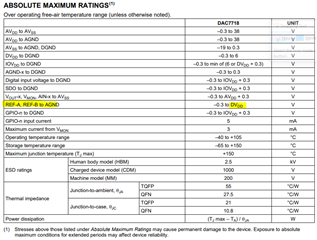

I am using the DAC7718SPAG on a board i have designed. I am seeing the VOUT-X lines go to about 9V after I release the reset line. This seems

strange as I expected them to remain at 0V.

I HAVE THE FOLLOWING ADDITIONAL INFO FOR THIS:

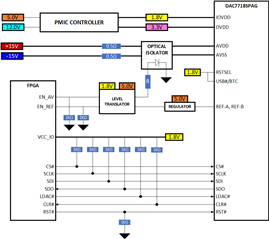

RSTSEL = USB#/BTC = IOVDD = 1.8V

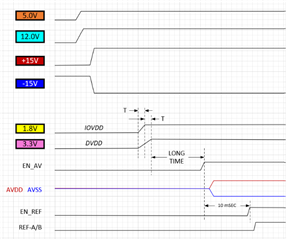

IOVDD = 1.8V (powered on first)

DVDD = 3.3V (powered on second)

AVDD = +15V (powered on third and simultaneous with) ... AVSS = -15V

REF-A = REF-B = 4.096V (powered on last)

According to the data sheet, this should configure the DAC as follows:

Dual-Supply

Twos Complement (input format)

VOUT = 0V (after RST# goes high)

However, I should mention that AVDD/AVSS/REF-A/B are all enabled by an FPGA. At this point, I am programming the FPGA

over JTAG. Once programmed, and once a jumper is manually removed, the logic automatically enables AVDD and AVSS, then

waits about 10 msec and enables REF-A / REF-B. So, there is a "human speed" time delay from IOVDD & DVDD to those three supplies

coming up.

Does that signal a red flag? The data sheet specifies supply sequencing but says nothing about required delay time between the

supplies.

Any insights and thoughts are appreciated. Thanks!