hello,

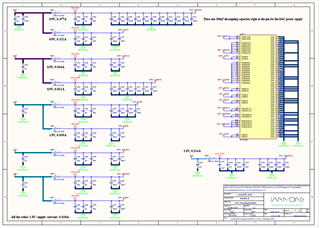

Is the data in the IBIS file required to match net length when running the JESD interface at 10 or 12Ghz? or is it sufficient to equalize just the traces to the DAC39J84 device from an FMC connector?

(ie will the JESD protocol be able to lock on without any lane errors)?

thanks again

Matthew