Hello,

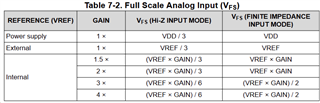

I am experimenting with the AFE539A4EVM and want to get confirmation on proper configuration to achieve different ADC V_FS (full scale analog Input) as shown in table.

It appears that when set for Hi-Z Input Mode and 4x Gain V_FS = (VREF * GAIN) / 6 like the table shows. However for Finite Impedance Input Mode and 4x Gain I get V_FS = (VREF * GAIN) which is not the same as the table which is 1/2 of this result.

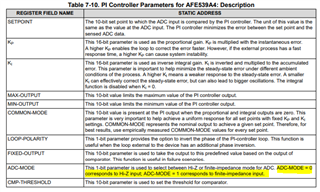

Please confirm proper way to set the registers

- for Hi-Z Input Mode and 4x Gain

- DAC-A-VOUT-CMP-CONFIG = 0x1405

- DAC-D-VOUT-CMP-CONFIG = 0x1405 (seems this unused D-channel needs to be set equal to A-channel)

- ADC-MODE 0x27[1] = 1

- for Finite Impedance Input Mode and 4x Gain

- DAC-A-VOUT-CMP-CONFIG = 0x1401

- DAC-D-VOUT-CMP-CONFIG = 0x1401 (seems this unused D-channel needs to be set equal to A-channel)

- ADC-MODE 0x27[1] = 0

Best,

Phil