Other Parts Discussed in Thread: AFE7900EVM, TSW14J57EVM, AFE7900

Hi,

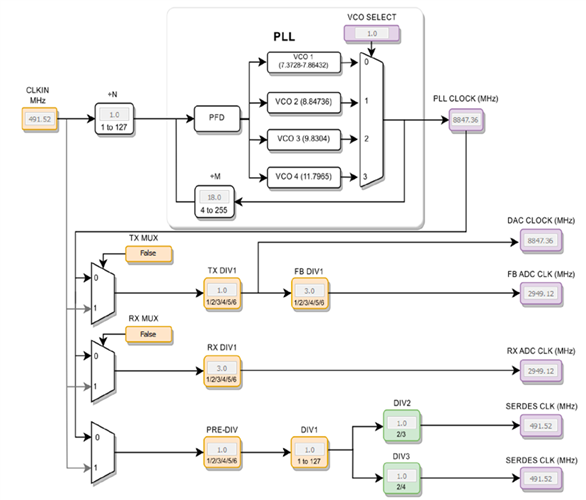

i'm trying to make small changes to one of TI's for AFE7900EVM standard configs and am running into a problem: the dynamic configuration window is not described in HSDC Pro User Guide, and when i'm trying to logically change some values, the TSW14J57EVM board starts to not capture data correctly and requires a firmware reboot. Please describe to me the parameters marked in attached screenshot so that i can achieve desired configuration.

Regards,

Oleg