Part Number: AMC1204

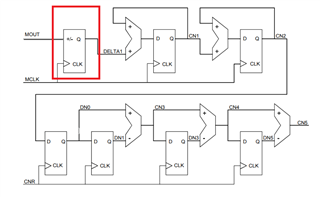

Hi guys, I am taking a look to SBAA094 and I don't understand behavior of sinc filter on VHDL code about input bitstream:

- ...000000... means -Vref

- ...111111... means +Vref

- ...0101010 ... means 0V

At reset DELTA1 is set to 0x00 (let's use hex notation), but while MOUT = 1, DELTA1 will be incremented.

No way to decrease DELTA1?

M=1 then DELTA = DELTA+1

Shouldn't be M=0 then DELTA = DELTA-1?

Thanks.