Dear Technical Support Team,

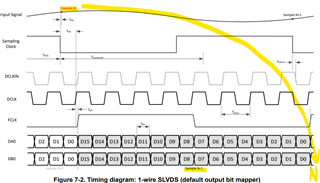

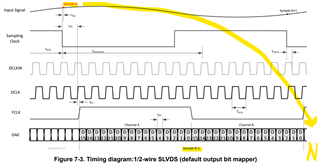

SLVDS for ADC3661 has 2-wire, 1-wire,1/2-wire output mode.

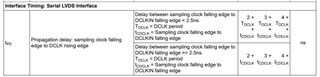

According to each timing diagram, is following output timing from sampling to Digital data correct?

10MSPS = 0.1us for sampling clock.

2-wire ⇒ (0.1us +tPD+tCD) * 2 from sampling to output

1-wire,1/2-wire ⇒0.1us+tPD+tCD from sampling to output

Best Regards,

ttd