Other Parts Discussed in Thread: DAC8742HEVM, DAC8742H

Hi,

I'm designing a 4-20mA loop-powered receiver that also needs to communicate as a HART device.

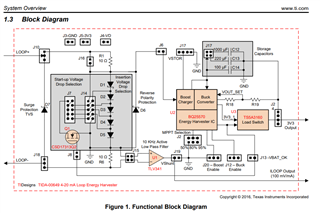

Since I am powering off the loop, I'm planning on having a series of diodes to get a fixed voltage drop across the 4-20mA terminals. Something in the range of 6-8V. I'll then have a small sense resistor (10-50 ohm is what I'm planning) in order to read the analog input signal.

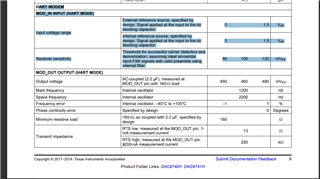

The issue that I'm trying to solve is how to make this work without a purely resistive input on the loop. Will tying the MOD_OUT and MOD_IN to the positive side of this diode network work? I don't anticipate any issue on the receiving portion but the transmission portion is where I have concern.

My input/power circuit will be similar in concept to this app note block diagram from TI:

Thoughts are appreciated!

-Brian