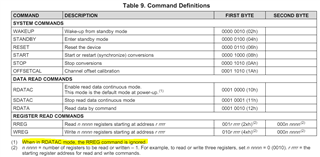

We have configured the ADS131E08S based on the ADS131E0X datasheet . Subsequently,

we have read the ADS131E08S registers on the board using the ST-Link V2, and here are the details:

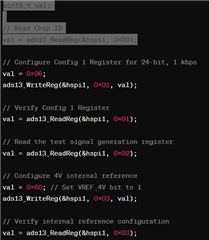

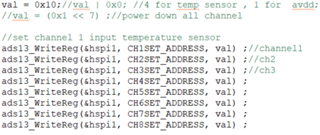

Readed ADS configuration regs :

1/ CONFIG 0 reg :

ID: ID Control Register

0x2d == 8 channel

2/ CONFIG 1 reg :

+ 0x91 (default): 16 bit resolution + 32 kbps data rate

1 0 0 1 0 001

+ 0x96 : 24 bit resolution + 1 kbps data rate

1 0 0 1 0 110

+ 0x92 : max speed : 24bit + 16 kbps data rate

1 0 0 1 0 010

----------------

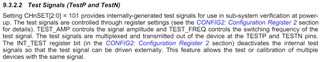

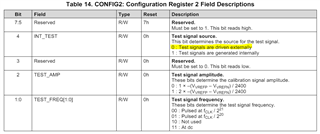

3/ Config 2 reg :

check value : 111 0 0 0 00 ==> signal amplitude. 0 : 1 × –(VVREFP – VVREFN) / 2400 ||| Test signal frequency. : Pulsed at fCLK / 2^21

4/ Config 3 reg :

0x60 = 0 1 1 0 0 0 0 0 ---> Power-down internal reference buffer + 4v vref + Noninverting input connected to the OPAMPP pin + Power-down op amp

-----------------------------

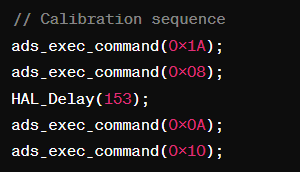

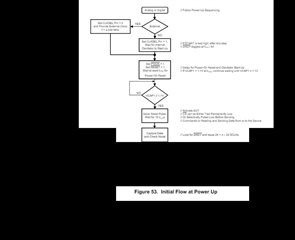

After the configuration of all configuration registers, and after checking and confirming that the register values are correct,

we have found that when we put the ADS in continuous mode, the ADS131E08S stops the conversion after some minutes.

is that a know issue ?

any idea about the cause ?.

best regards