Other Parts Discussed in Thread: LMK00304, LMX2594, LMK04828

Hello!

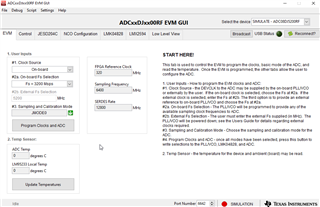

A bit of relevant EVM configuration information:

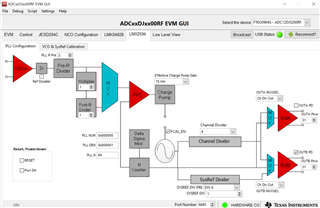

We are using the external reference clocking option and have the hardware configured accordingly.

We have a signal generator providing 400 MHz @ 6 dBm to the LMK00304 chip that duplicates the 400 MHz signal to be provided as Fosc for the LMX2594 & CLKin1 to the LMK04828B.

The LMK04828 is outputting clocks as expected to the FPGA:

- 200 MHz LVDS on DCLKout0

- 10 MHz LVDS SYSREF on SDCLKout1

- 200 MHz LVDS on DCLKout12, which the FPGA is internally generating as the 320 MHz JESD core clock

The LMX is configured to output a 3200 MHz clock signal from RFoutA, and it is confirmed to be locking: when reading back register 0x6E (R110) we are reading 0x4A8, also indicating that the calibration is occurring on the right VCO_SEL.

The LMK04828 is passing a 10 MHz SYSREF on SDCLKout13 to the SYSREFREQ pin of the LMX, which has SYSREF enabled in repeater mode, but the RFoutB output is currently powered down, not providing any SYSREF to the ADC.

The ADC is being configured in accordance with the Initialization Set Up procedure detailed in section 8.3 of the data sheet:

0x00000080, // soft reset - 3

0x00020000, // JESD_EN = 0 --> disable jesd transceiver - 4

0x00006100, // CAL_EN = 0 --> disable calibration - 5

0x00020100, // JMODE = 0 (single channel, 8 lanes) - 6

0x00020207, // KM1 = 7 => K = 8 - 7

0x00020301, // JSYNC_N

0x00020403, // Enable scrambler for 8B/10B mode & signed 2's comp - 8

0x00006101, // CAL_EN = 1 --> enable calibration - 10

0x00020505, // test pattern mode: Transport

0x00020702, // FCHAR K28.5

0x00020001, // JESD_EN = 1 --> enable jesd transceiver - 12

0x00006C00, // CAL_SOFT_TRIG = 0 - 14

0x00006C01 // CAL_SOFT_TRIG = 1 --> enables a calibration - 15

Result:

On the EVM, we configure the LMK, LMX, then the ADC itself. Then reading the JESD status register 0x208 of the ADC to check the PLL lock status--it returns 0!

I am looking for advice on the steps to take here to fix this issue so the ADC PLL can lock and then we can move forward to see the JESD link go up.

Thanks in advance!