Hello!

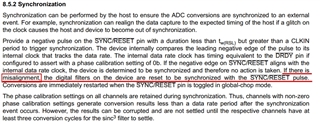

In this paper, when SYNC is misaligned with the internal data rate clock, does the "misalignment" mean that the internal data rate clock and SYNC are not multiples of each other?

To synchronize the digital filter reset with the pulse of SYNC, is it the internal data rate clock or the frequency of DRDY?

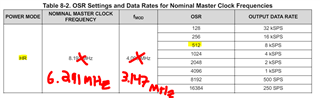

If is the frequency of DRDY and is synchronized with SYNC, is the frequency of SYNC and the frequency of DRDY an integer multiple relationship?