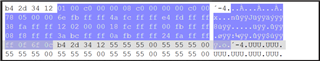

I just realized my ADC redings are multiples of ten, I have 4vref with 16ksps G=1. Do u know the reason?

| -103090 | -135290 | -139770 | -120230 | -215080 | -260580 | -275800 | -316370 | 80970 | -240960 |

| -103000 | -134660 | -140190 | -121890 | -214070 | -260570 | -274090 | -317660 | 78670 | -245910 |

| -102790 | -133920 | -140960 | -123220 | -212930 | -260420 | -272430 | -319020 | 76340 | -251100 |

| -102520 | -133400 | -141570 | -124660 | -211810 | -260150 | -270800 | -320190 | 73940 | -255970 |

| -102380 | -132770 | -142180 | -126010 | -210580 | -260040 | -268800 | -321230 | 71350 | -261000 |

| -102270 | -132230 | -142840 | -127360 | -209480 | -259610 | -267000 | -322220 | 68690 | -265690 |

| -102090 | -131390 | -143470 | -128880 | -208240 | -259220 | -265160 | -322920 | 65860 | -270500 |

| -101920 | -130800 | -144150 | -130260 | -207090 | -258870 | -262930 | -323750 | 63320 | -275360 |