Other Parts Discussed in Thread: DAC38RF82

Hello,

I am evaluating DAC38RF82 with the evaluation board and the pattern generator.

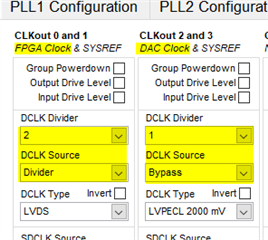

A 100 MHz / +6dBm signal is fed to the input of the LMK (J4 connector).

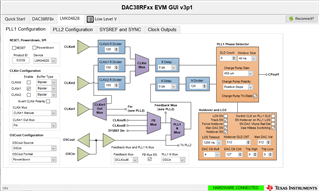

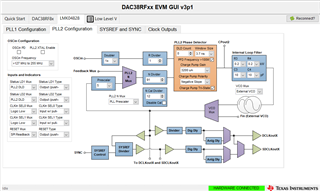

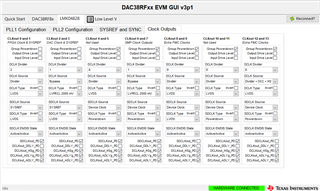

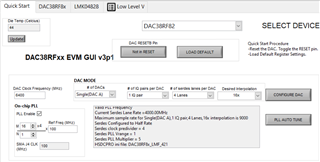

With the following configuration (only one DAC), all is right, a correct spectrum is present at the output of the DAC.

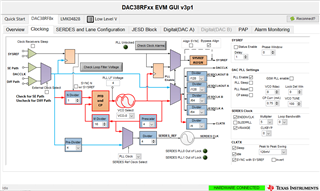

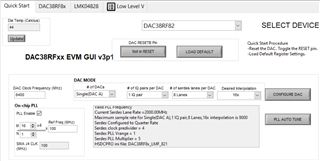

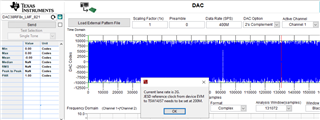

When the configuration is changed to 8 lanes (instead of 4 lanes), the Serdes Lane Rate is twice lower, there is no other configuration change than the HSDCPRO file (suffix 821 instead of 421) :

On the HSDCPRO GUI, when loading the right ini file (suffix : 821), the following pop-up message appears:

And after resetting DAC JESD Core (DAC GUI), it is not possible to have a spectrum at the DAC output (no signal at all).

I suppose that this is due to the JESD reference clock (to TSW14J57) which has to be set to 200 MHz (instead of 100 MHz).

What is wrong with this configuration ?