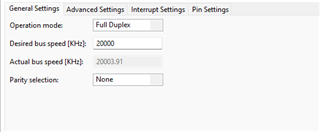

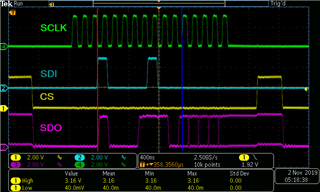

I've added snippets of code and SPI configs for review.

Please help as I'm new to this.

For loop in code snippet refers to the delay. We have tested the code with and without delay still we're not receiving any data in receive buffer.

uint8_t send_addr[4] = {0x10, 0x80, 0x10, 0x00};

uint8_t receive_data[4] = {0};

//----------------xx MANUAL MODE xx --------------------------------------------------------------------

//------------------------------------------------------------------------------------------------------

DIGITAL_IO_SetOutputLow(&DIGITAL_IO_0);

//90,000 10ms

//9000 1ms

//100 ns

// for(uint16_t delay = 0; delay < 2; delay++);

SPI_MASTER_Transmit(&SPI_MASTER_0, &send_addr[0], 1);

while(SPI_MASTER_0.runtime->tx_busy);

SPI_MASTER_Transmit(&SPI_MASTER_0, &send_addr[1], 1);

while(SPI_MASTER_0.runtime->tx_busy);

// for(uint16_t delay = 0; delay < 100; delay++); //50ns

DIGITAL_IO_SetOutputHigh(&DIGITAL_IO_0);

//------------------------------------------------------------------------------------------------------

DIGITAL_IO_SetOutputLow(&DIGITAL_IO_0);

//90,000 10ms

//9000 1ms

//100 ns

// for(uint16_t delay = 0; delay < 2; delay++); //50ns

SPI_MASTER_Transmit(&SPI_MASTER_0, &send_addr[2], 1);

while(SPI_MASTER_0.runtime->tx_busy);

SPI_MASTER_Transmit(&SPI_MASTER_0, &send_addr[3], 1);

while(SPI_MASTER_0.runtime->tx_busy);

SPI_MASTER_Receive(&SPI_MASTER_0, &receive_data[0], 2);

while(SPI_MASTER_0.runtime->rx_busy);

// for(uint16_t delay = 0; delay < 100; delay++); //50ns

DIGITAL_IO_SetOutputHigh(&DIGITAL_IO_0);

//------------------------------------------------------------------------------------------------------

DIGITAL_IO_SetOutputLow(&DIGITAL_IO_0);

//90,000 10ms

//9000 1ms

//100 ns

// for(uint16_t delay = 0; delay < 2; delay++); //50ns

SPI_MASTER_Transmit(&SPI_MASTER_0, &send_addr[0], 1);

while(SPI_MASTER_0.runtime->tx_busy);

SPI_MASTER_Transmit(&SPI_MASTER_0, &send_addr[1], 1);

while(SPI_MASTER_0.runtime->tx_busy);

SPI_MASTER_Receive(&SPI_MASTER_0, &receive_data[0], 2);

while(SPI_MASTER_0.runtime->rx_busy);

// for(uint16_t delay = 0; delay < 100; delay++); //50ns

DIGITAL_IO_SetOutputHigh(&DIGITAL_IO_0);

//------------------------------------------------------------------------------------------------------