Hello,

It appears that, in some cases, the ADC is sending incorrect data over the LVDS interface.

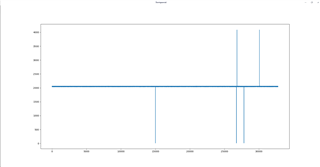

Here is an example of noise acquisition with the presence of incorrect data (temporal view) using dual-channel mode and 3.2Gsps, processed by a Ultrascale+ FPGA.

We believe that the sample is incorrect at the output of the ADC, and this issue is not related to the LVDS interface management by the FPGA.

The voltage, temperature, and clock level values have been checked without detecting any issues.

We are looking for ideas to help us move forward with our investigation.

Best regards