Other Parts Discussed in Thread: DAC38RF82,

Hello,

I am evaluating DAC38RF82 with the evaluation board (DAC38RF82EVM) and the TSW14J57 pattern generator with high data rate.

A 1100 MHz / +6dBm signal is fed to the input of the LMK (J4 connector).

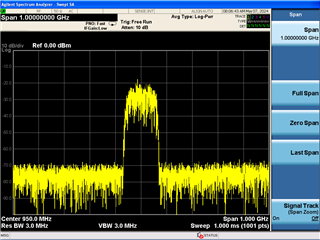

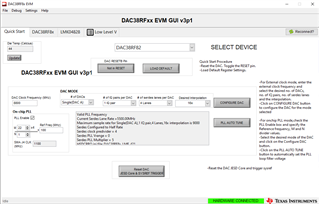

With the following configuration (Data Rate is 550 MSPS), all is right, it is possible to get a correct signal (about 400 MHz bandwidth) at the DAC output.

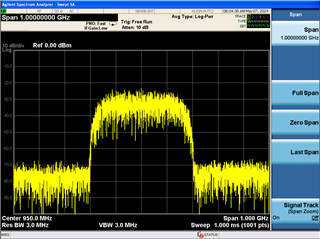

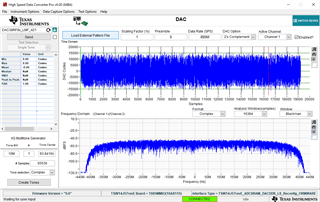

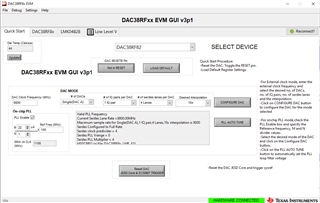

In order to get higher bandwidth signal, the following configuration is used (interpolation changed from x16 to x10, data rate is now 880 MSPS):

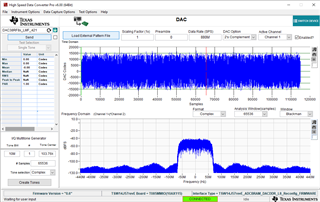

A file is sent to the TSW14J57 board (bandwidth about 140 MHz to begin), in frequency domain, the following spectrum is shown:

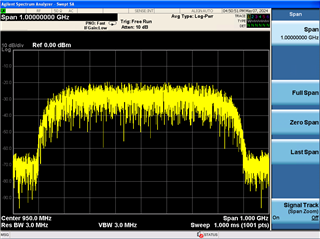

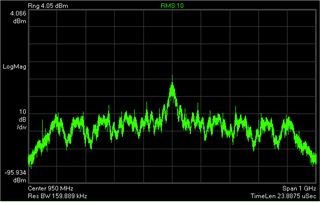

But, this time, after loading the file, the signal at the DAC output is not correct:

Here are the clock configurations (LMK and DAC):

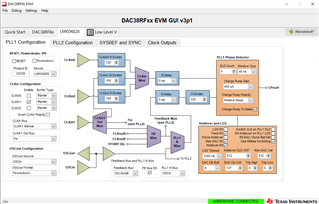

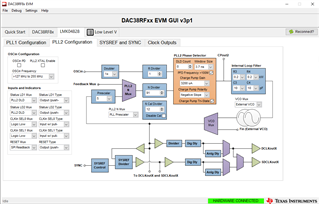

PLL1:

PLL2:

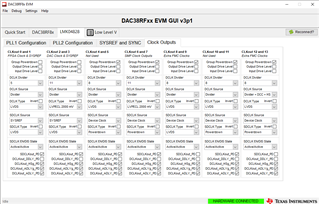

Clock Outputs:

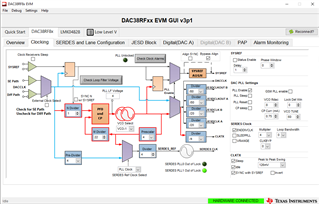

DAC Clocking:

Is there any limitation ?

Thanks for your help.