Hello,

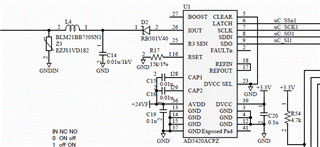

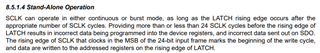

My customer has replaced AD5420 with DAC8750 since those are P2P compatible, but it seems it has written data to an unexpected register at the event occurring both alarm set and data send at the same time. AD5420 seems to make the data invalid at the event, but would you please tell me how DAC8750 is expected to behave at that event? How my customer should do for that event? I looked at the datasheet, apps notes and E2E, but I wasn't able to find the information for that.

Best Regards,

Yoshikazu Kawasaki