Part Number: AFE5816

Hello, everyone

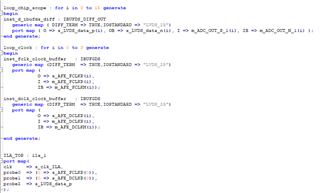

I am trying to verify the output from the AFE using a test pattern. I want to check the output data through ILA, and the clocks are as follows: ILA clock = 280MHz AFE input clock = 10MHz It is set to 14bit 1X serialization.

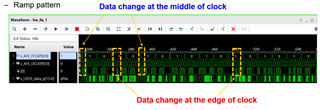

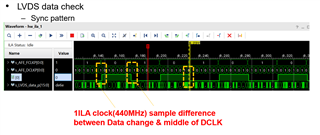

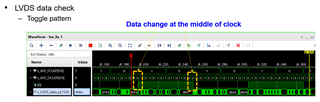

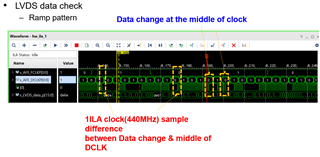

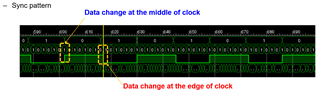

In the toggle pattern, as in the datasheet, we can see that the data changes at the center of DCLK. However, in the ramp and sync, some of the data was observed to change at the edge of DCLK. What could be the potential problem and solution?

1) SYNC pattern (works wrong)

2) Toggle pattern (works well)

3) RAMP pattern (works wrong)