Other Parts Discussed in Thread: LMX2594, LMK04832

Hello,

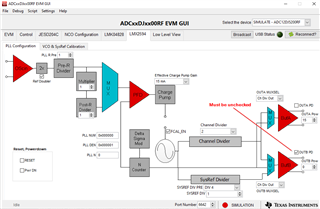

I am using the adc12dj5200 chip to generate a 10G sampling rate.The ADC's configuration is jmode0,K=4,sysref = 31.25MHz,lane_rate=10Gbps.The sampling clock of ADC is generated by RoutA of LMX2594, and sysref is generated by RoutB.The fosc of lmx2594 is 100MHz which is generated from lmk04832.The register configurations for the three chips are as follows:

LMK04832

R0 (INIT) 0x000090 R0 0x000000 R2 0x000200 R3 0x000306 R4 0x0004D0 R5 0x00055B R6 0x000600 R12 0x000C51 R13 0x000D04 R256 0x010001 R257 0x01010A R258 0x010250 R259 0x010344 R260 0x010420 R261 0x010522 R262 0x010600 R263 0x010710 R264 0x010819 R265 0x01090A R266 0x010A10 R267 0x010B64 R268 0x010C00 R269 0x010D22 R270 0x010E00 R271 0x010F11 R272 0x011018 R273 0x011155 R274 0x011210 R275 0x011300 R276 0x011420 R277 0x011500 R278 0x0116F0 R279 0x011710 R280 0x01180A R281 0x01190A R282 0x011A10 R283 0x011B64 R284 0x011C00 R285 0x011D00 R286 0x011E00 R287 0x011F11 R288 0x01200A R289 0x01210A R290 0x012210 R291 0x012344 R292 0x012400 R293 0x012500 R294 0x012600 R295 0x012710 R296 0x01280A R297 0x01290A R298 0x012A10 R299 0x012B44 R300 0x012C00 R301 0x012D00 R302 0x012E00 R303 0x012F10 R304 0x01300A R305 0x01310A R306 0x013210 R307 0x013344 R308 0x013400 R309 0x013500 R310 0x013600 R311 0x013711 R312 0x013800 R313 0x013903 R314 0x013A00 R315 0x013B50 R316 0x013C00 R317 0x013D00 R318 0x013E03 R319 0x013F0D R320 0x014000 R321 0x014100 R322 0x014200 R323 0x014311 R324 0x0144FF R325 0x01457F R326 0x01463C R327 0x01471A R328 0x014802 R329 0x014902 R330 0x014A03 R331 0x014B16 R332 0x014C00 R333 0x014D00 R334 0x014EC0 R335 0x014F7F R336 0x015003 R337 0x015102 R338 0x015200 R339 0x015300 R340 0x015404 R341 0x015500 R342 0x015608 R343 0x015700 R344 0x015801 R345 0x015900 R346 0x015A19 R347 0x015BD4 R348 0x015C20 R349 0x015D00 R350 0x015E00 R351 0x015F0B R352 0x016000 R353 0x01610A R354 0x0162AC R355 0x016300 R356 0x016400 R357 0x016532 R361 0x016959 R362 0x016A20 R363 0x016B00 R364 0x016C00 R365 0x016D00 R366 0x016E13 R371 0x017310 R375 0x017700 R386 0x018200 R387 0x018300 R358 0x016600 R359 0x016700 R360 0x016832 R1365 0x055500

The sync pin signal of lmx2594 is provided by sdclkout1 of lmk04832, with a frequency of 31.25MHz The SYSREFREQ pin signal is provided by sdclkout5 at a frequency of 31.25MHz.

LMX2594 CONFIGURATION:

R112 0x700000 R111 0x6F0000 R110 0x6E0400 R109 0x6D0000 R108 0x6C0000 R107 0x6B0000 R106 0x6A0000 R105 0x690021 R104 0x680000 R103 0x670000 R102 0x660000 R101 0x650011 R100 0x640000 R99 0x630000 R98 0x620000 R97 0x610888 R96 0x600000 R95 0x5F0000 R94 0x5E0000 R93 0x5D0000 R92 0x5C0000 R91 0x5B0000 R90 0x5A0000 R89 0x590000 R88 0x580000 R87 0x570000 R86 0x560000 R85 0x550000 R84 0x540000 R83 0x530000 R82 0x520000 R81 0x510000 R80 0x500000 R79 0x4F0000 R78 0x4E0003 R77 0x4D0000 R76 0x4C000C R75 0x4B0800 R74 0x4A0000 R73 0x49003F R72 0x480008 R71 0x470049 R70 0x460000 R69 0x450000 R68 0x4403E8 R67 0x430000 R66 0x4201F4 R65 0x410000 R64 0x401388 R63 0x3F0000 R62 0x3E0322 R61 0x3D00A8 R60 0x3C03E8 R59 0x3B0001 R58 0x3A9001 R57 0x390020 R56 0x380000 R55 0x370000 R54 0x360000 R53 0x350000 R52 0x340820 R51 0x330080 R50 0x320000 R49 0x314180 R48 0x300300 R47 0x2F0300 R46 0x2E07FE R45 0x2DC0DF R44 0x2C1F20 R43 0x2B0000 R42 0x2A0000 R41 0x290000 R40 0x280000 R39 0x270001 R38 0x260000 R37 0x250104 R36 0x240032 R35 0x230004 R34 0x220000 R33 0x211E21 R32 0x200393 R31 0x1F43EC R30 0x1E318C R29 0x1D318C R28 0x1C0488 R27 0x1B0002 R26 0x1A0DB0 R25 0x190C2B R24 0x18071A R23 0x17007C R22 0x160001 R21 0x150401 R20 0x14D848 R19 0x1327B7 R18 0x120064 R17 0x11012C R16 0x100080 R15 0x0F064F R14 0x0E1E30 R13 0x0D4000 R12 0x0C5001 R11 0x0B0048 R10 0x0A10D8 R9 0x091604 R8 0x082000 R7 0x0740B2 R6 0x06C802 R5 0x0500C8 R4 0x040A43 R3 0x030642 R2 0x020500 R1 0x010808 R0 0x006418

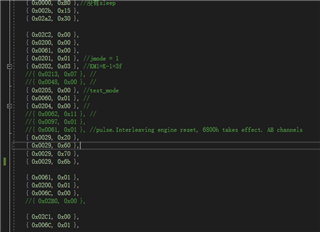

adc12dj5200 configuration:

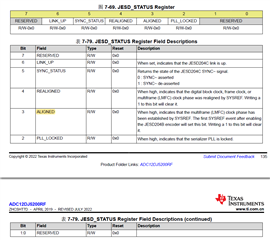

After configuring three chips according to the above file, I read back the value of register 0x038 in JESD204b core in FPGA, which is 0x10001, and the value of 0x03c is eeee, indicating that the link of jesd204b has been established normally. But when I read back register 0x208 in adc12dj5200, the value I read back is 0x64, which indicates that the phase of LMCF and sysref is not aligned.Can you help me solve this problem?

Regards,

xiaxin