HI team ,

I am Working in the project of data acquisition system so we need 8 channel input in this case we choose the ADS1278. To configer the ADS1278 through the SPI protocol,

we are configer the configeration through the I/O pins

ADS1278 Input Pin -TEST pin[0:1] //this pins are set to LOW Because we use Normal Mode.

ADS1278 Input Pin -FORMAT pin[0:2] // this pins are set to LOW Because we use SPI TDM Dynamic formate.

ADS1278 Input Pin -MODE pin[0:1] //this pins are set to LOW Because we use High-Speed Mode.

ADS1278 Input Pin -POWER DOWN pin[0:8] //this pins are set to HIGH Because we use 8 Channel of input.

ADS1278 Input Pin -CLKDIV pin 1 //this pins are set to HIGH Because we need Higher sample per Second.

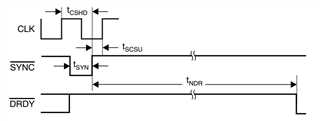

ADS1278 Input Pin -CHIP SELECT/SYNC pin 1 //this pins are set to HIGH OR LOW(Based on the condition).

ADS1278 Output Pin -DRDY pin 1 //Read the pin.

FCLK=25MHz

SCLK=25MHz

After the configeration

First CHIP SELECT/SYNC pin put low

After monitering the DRDY pin //When the pin is Low ....Move the next condition.

In spi write 24 Bytes data=0 will send / Also 24 Bytes of SCLK will also send.

But SPI Read function there is no data is recived

CHIP SELECT/SYNC pin put HIGH...... In this time DRDY pin is gose to High

HOW to Retrieve the data....?

Please give me a reference code.

Thanks and Regards,

Aravind.SR