Other Parts Discussed in Thread: AFE7951, AFE7950, , AFE7906, DAC39RF12, DAC39RF10, DAC38RF89

We are currently developing a direct conversion solution in the X band, and for that, we need to use high-speed DAC and ADC converters, such as: AFE7906, AFE7950, AFE7951, DAC39RFS12.

We need to know which JESD204B/C modes these converters can be configured. This information will be greatly appreciated as it will help us size our system according to the number of conversion channels we will need.

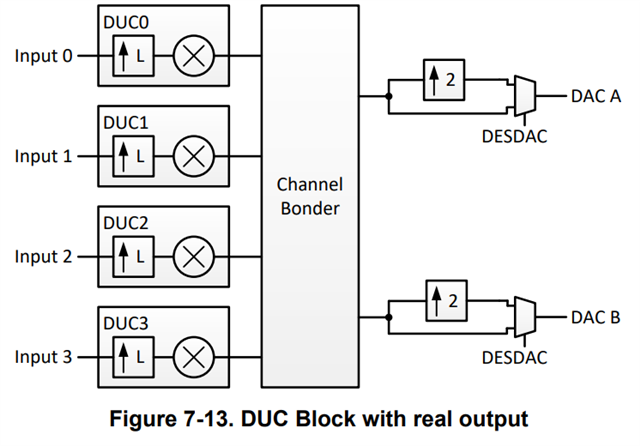

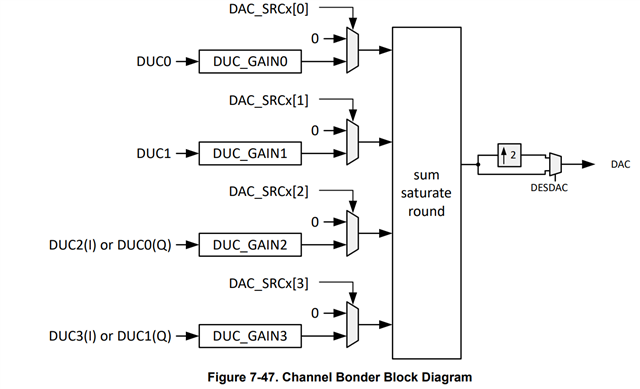

Another question about these converters is regarding the relationship between the digital signals in phase and quadrature, and the analog output signals. In one converter, I noticed that there is the possibility for 4 pairs of digital signals (CH0_I, CH0_Q, CH1_I, CH1_Q, CH2_I, CH2_Q, CH3_I, and CH3_Q) to be transported by the JESD204B/C LANES, however, there are only 2 analog conversion outputs (DACOUTA+, DACOUTA-, DACOUTB+, and DACOUTB-). How does the digital signal relate to the analog signal? For example, do channels CH0_I and CH0_Q control the phase and amplitude of the analog output DACOUTA+.