Other Parts Discussed in Thread: ADS54J60

Hello,

We are trying to configure our ADS54J69 on our custom FMC board. With an oscilloscope we see data coming from the FPGA to the ADC on the SDIN line, we see the correct SPI clock on SCLK, and our reset line is behaving correctly.

However, we are not seeing any data on SDout which is telling us the ADC is unresponsive.

We are writing these values to the registers to set the ADC to LMFS-4211:

// FMC231 ADS54J60 settings

// LMFS = 4211 no Decimation mode. this mode is only for ADS54J60. JESD204 lane 0 = DA1; lane 1 = DA2

static spi_bus_t ads54j60_4211_init_regs[] =

{

// register writes reset

{{0x00, 0x00}, 0x81}, // Reset registers in the ADC and master pages of the analog bank.

{{0x40, 0x01}, 0x00}, // Clear any unwanted content from the unused pages of the JESD bank.

{{0x40, 0x02}, 0x00}, // Clear any unwanted content from the unused pages of the JESD bank.

{{0x40, 0x03}, 0x00}, // Select the main digital page of the JESD bank.

{{0x40, 0x04}, 0x68}, // Select the main digital page of the JESD bank.

{{0x60, 0xF7}, 0x01}, // Use the DIG RESET register bit to reset all pages in the JESD bank.

{{0x60, 0x00}, 0x01}, // Set PULSE RESET register bit for channel A

{{0x60, 0x00}, 0x00}, // Cler PULSE RESET register bit for channel A

// performance mode

{{0x00, 0x11}, 0x80}, // Select the master page of the analog bank.

{{0x00, 0x59}, 0x20}, // Set the ALWAYS WRITE 1 bit.

// Select the JESD digital page

{{0x40, 0x04}, 0x69}, // Select the JESD digital page

{{0x40, 0x03}, 0x00}, // Select the JESD digital page

// Select the CTRL K bit

{{0x60, 0x00}, 0x80}, // Set the CTRL K bit for both channels by programming K according to the SYSREF signal later on in the sequence.

// enable scrambling

{{0x60, 0x05}, 0x80},

// K=32

{{0x60, 0x06}, 0x1F}, // Frames per multifame

// Select the digital to 40x mode

{{0x60, 0x01}, 0x04}, // Four lanes are active, no decimation (filter bypass), Use the SYNC pin for sync requests, Normal operation

//Or test mode

// {{0x60}, {0x01}}, {0x84}, // Four lanes are active, no decimation (filter bypass), Use the SYNC REG register bit for sync requests, ADC output data are replaced with K28.5 characters.

// Select the JESD analog page

{{0x40, 0x04}, 0x6A},

{{0x40, 0x03}, 0x00},

// Set the SERDES PLL to 40x mode

{{0x60, 0x16}, 0x02},

// PLL reset

{{0x60, 0x17}, 0x40}, // PLL reset set

{{0x60, 0x17}, 0x00}, // PLL reset clear

/* // transmitter amplitude

{{0x60, 0x1B}, 0x60}, //[7:5] JESD swing. 0=860mV 1=810 2=770 3=745 4=960 5=930 6=905 7=880 [3] FOVR CHA en

// de-emphasis

{{0x60, 0x12}, 0x04}, //[7:2] de-emphasis 0=0dB; 1=-1 3=-2 7=-4.1 F=-6.2; 1F=-8.2 3F=-11.5

{{0x60, 0x13}, 0x04},

{{0x60, 0x14}, 0x04},

{{0x60, 0x15}, 0x04},

*/

// Select the main digital page

{{0x40, 0x04}, 0x68},

{{0x40, 0x03}, 0x00},

// Pulse the PULSE RESET regiter bit

{{0x60, 0x00}, 0x01}, // Pulse the PULSE RESET register bit. All settings programmed in the main digital page take effect only after this bit is pulsed.

{{0x60, 0x00}, 0x00}, // Pulse the PULSE RESET register bit. All settings programmed in the main digital page take effect only after this bit is pulsed.

{{0x00, 0x00}, 0x00} // The last

};

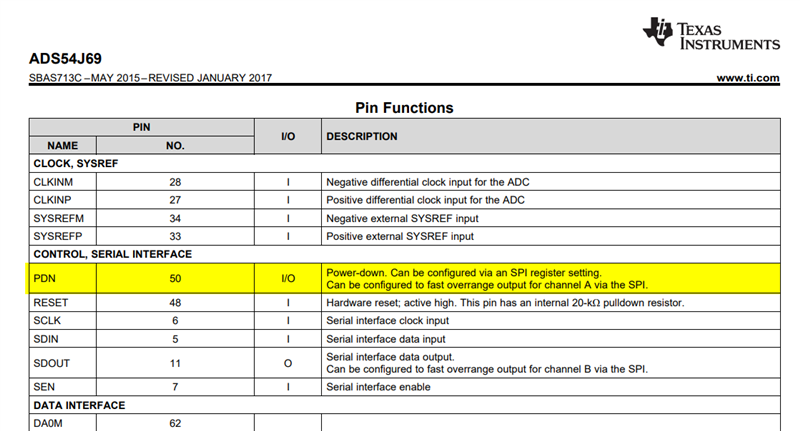

Our PDN pin is tied high in our design and our firmware and SPI settings above do not address this pin and we are not planning to use the power down mode.

Can the settings above be checked and is there anything that needs to be done with the PDN pin?

Thank you,

Ryan