Part Number: ADS52J90

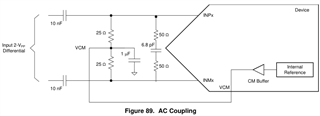

I can't find this one being asked previously. I am interfacing the ADS52J90 inputs to 100Ω differential (Zdiff) analog outputs from another device. The datasheet figure 89 is as follows but I don't understand why it has both 100Ω and 50Ω termination. I believe it is both terminating a 50Ω pair with VCM, and showing 100Ω termination as well (not necessary to do both)? If both are intended to be present then this would present a impedance mismatch.

Figure 90 of the datasheet (DC coupling) shows just the 100Ω termination.

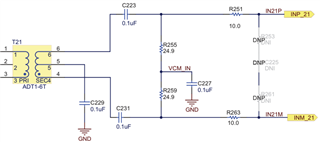

I've derived this based on the EVM schematic including 50Ω termination fitted as it includes ADT1-6T (1:1 50Ω) baluns:

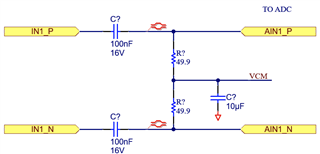

I have used basically the EVM circuit (without the 50Ω resistors and 6.8pF cap) but changed the 24.9Ω resistors to 49.9Ω for my 100Ω Zdiff system, as shown below (representative of my system). Is this not the right way to terminate the diff pair and inject VCM?