Tool/software:

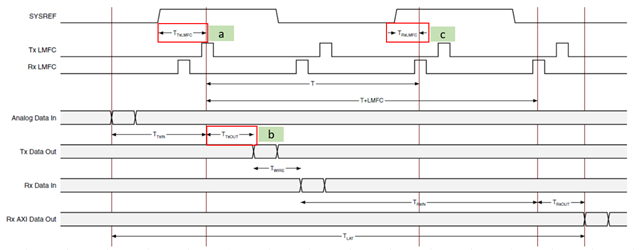

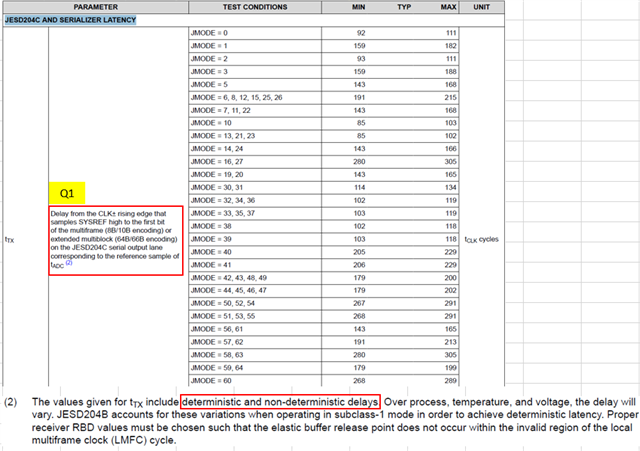

The figure upper is from ADC12DJ5200RF datasheet(P30, 6.10).With about the tTx,in my opinion the non-deterministic delays(b) is the delay from TxLMFC to JESD204 serail output.And the deterministic delays(a) is the fixed delay from SYSREF to TxLMFC.How can I know the deterministic(a)?OR I can use it as same as the the fixed delay(c) in FPGA from SYSREF to RxLMFC .

The figure below URL: https://ez.analog.com/cfs-file/__key/telligent-evolution-components-attachments/00-423-01-00-00-19-60-57/pg066_2D00_jesd204.pdf