Tool/software:

Hello

I am designing a pcb where I want to connect 2 ADS127L11 in daisy-chain mode.

I am looking at ADS127L11 in Simultaneous-Sampling Systems and the TIDA-010249.

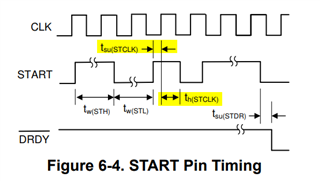

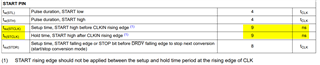

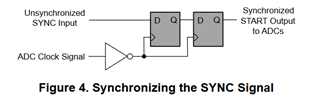

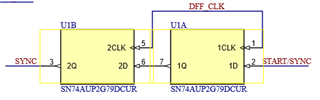

In the Simultanoues Sampling Documen ADC clock is inverted in the start/sync synchronziation circuit. Which makes sense as we want the Flip Flops to trigger on the falling edge of the clock, to get rid of the 1 cycle uncertainty.

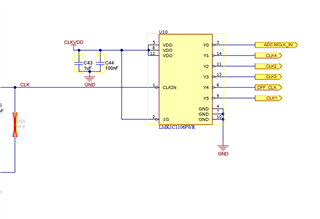

However in the schematics of the reference design, no such inversion takes place.

Am I missing something? Or is there an error in the Reference design?

And why are 2 D-Flip-Flops used at all? Wouldn't 1 suffice?

Thanks for your help