Tool/software:

Hello,

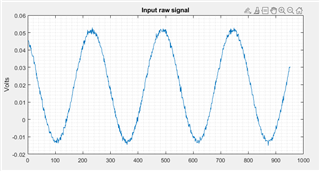

We are using ADS1282 and would like to estimate base line (noise floor) and having issues with output data.

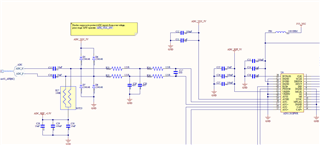

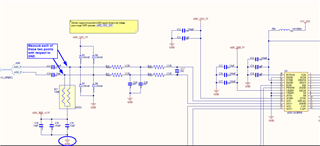

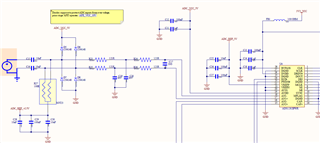

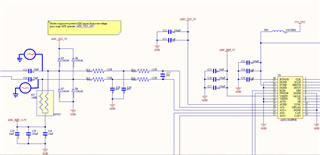

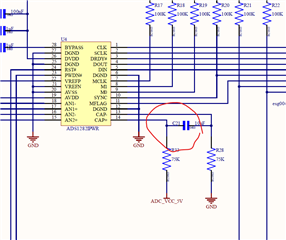

Hardwire configuration:

ADC reference set to 5V DC

AIN1+, AIN1- is connected via 121R to 2.5V reference voltage

ADC clock set at 4.096MHZ

Software Configuration

Config 0 register is configured to 0xD9

D7 1 continuums SYNC mode

D6 1 reserved

D5:D3 001 64KHZ data rate Table6 page 18

D2 0 Linear phase

D1: D0 01 Sinc Filter is selected

Other registers left at default state

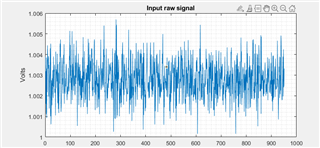

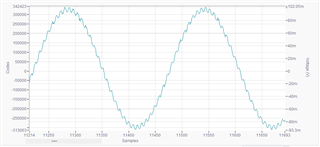

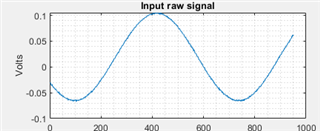

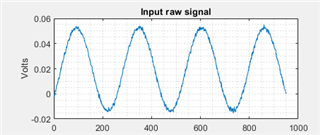

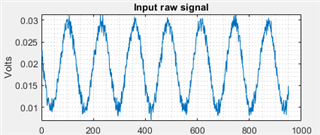

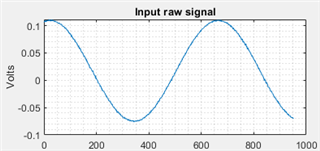

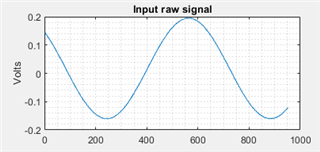

When reading 32 bit data , we expecting data to be near 0 , according to the table 13 page 26 data sheet,

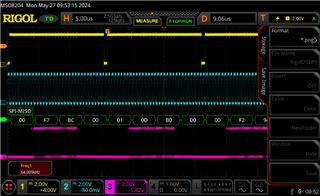

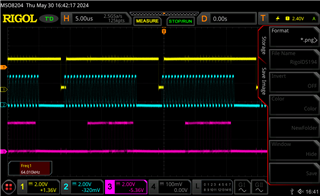

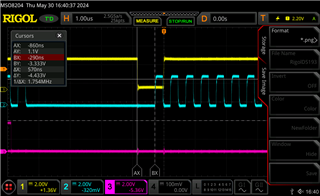

but we are getting relatively large noise floor, please see attached scope plot. Yellow line is ADC RDY ; blue SPI CLK; magenta is SPI Data Out from ADC.

Could you please advise what can be wrong?

Thank you,

Iouri