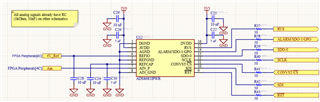

Other Parts Discussed in Thread: ADS8685

Tool/software:

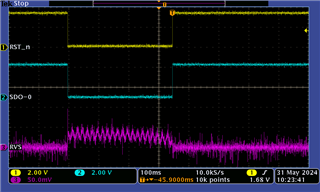

This is my first use of the device. All grounds are connected to the same return plane. Upon initial power-up or reset (RST_n pin driven to 3.3V), the RVS pin remains low. According to section 7.4.2.1 of the datasheet: "In order to exit any of the RESET states, the RST pin must be pulled high with CONVST/CS and SCLK held low. After a delay of tD_RST_POR or tD_RST_APP, the device enters ACQ state and the RVS pin goes high." I read this to mean that CONVST/CS should remain low, along with SCLK until RVS goes high. Please advise.

Please advise. I am driving the device with an FPGA using 3.3V I/O.

DGND = 0V

AVDD = 5.2V

AGND = 0V

REFIO = ~4.09V

REFGND = 0V

REFCAP = ~4.09V

AIN_P = Unconnected

AIN_GND = 0V

RST_n = 0V or 3.3V

SDI = 0V

CONVST/CS_n = 0V (FPGA is waiting for RVS to go high before starting a conversion)

SCLK = 0V

SDO-0 = 0V when RST_n = 0V; 3.3V when RST_N = 3.3V

ALARM/SDO-1/GPO = 0V

RVS = 0V

DVDD = 3.3V