Tool/software:

Hi,

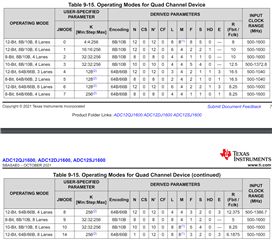

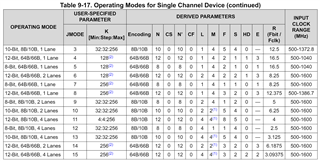

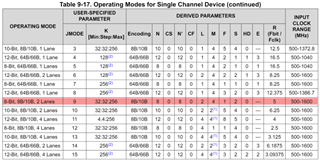

I would like to configure Microchips JESD204B core for PolarFire FPGAs together with the ADC12QJ1600 ADC.

A limitation in hardware is that I only have a maximum of 4 lanes connected to the FPGA.

First step is to setup the ADC with only one core (A) enabled and the other cores (B, C, D) powered down.

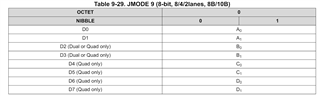

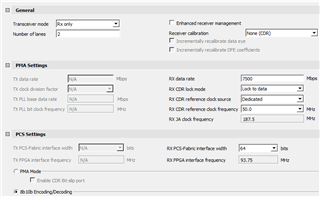

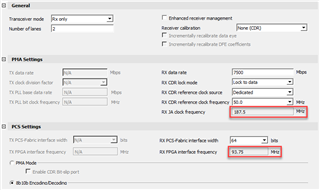

If I select JMODE9 (8-bit, 2 lanes, 8B/10B encoding), how should I configure the FPGA JESD core?

/Mikael