Tool/software:

Hi team,

I am working the project of 8 channel DAQ for using the ADS1278.

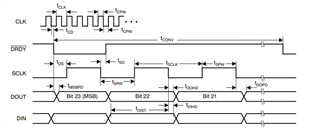

Configure the high speed mode for sampling at 65536SPS_FCLK_16.777MHZ.

Next enable the 4 channel and Using the spi protocol for read the ADC data.

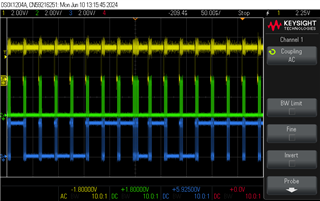

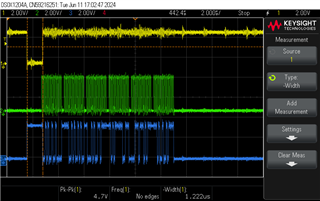

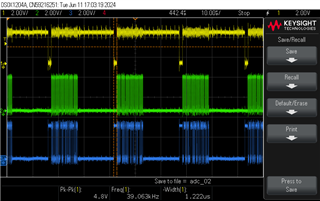

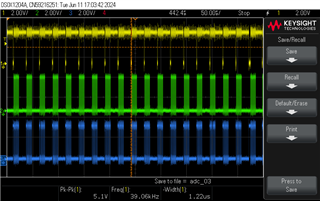

SPI read using 16 bit mode.It's take 6 cycle(6 x 16) = 96 clock pulse_4 channel x 24 bit = 96 bit .ADC reading by SPI _TDM Mode(Dynamic Position Data).

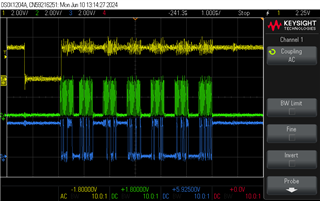

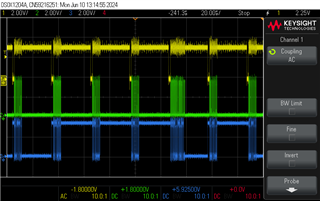

1st and 3rd channel data output correctly as per the input signal

But 2nd and 4th Channel output is aliasing with some noise,But input for all the 4 channel is given from one same source.

How to solve the issue.!

And ,I will read the 2nd,3rd and 4th.In that time 2nd and 4th channel is correct .3rd channle aliasing with some noise.

SPI reading settup

for(data = 0; data < 6; data++)

{

SSIDataPut(SSI0_BASE, 0);

SSIDataGet(SSI0_BASE, &SPI_Data[data]);

HF_msg[i++] = (SPI_Data[data] >> 8) & 0xFF;

HF_msg[i++] = SPI_Data[data];

}

Thanks and Regards,

Aravind