Tool/software:

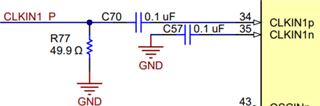

The T10 used for an external reference clock was intended as follows:

However, what you soldered was the Minicircuit part TC1-1-13M+

Which has following connection:

In order to get the functionality as shown in the schematic the transformer has to be turned.