Other Parts Discussed in Thread: DAC39J82

Tool/software:

Hello TI support,

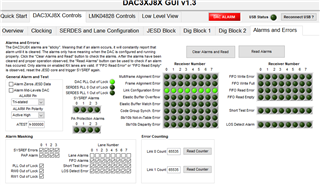

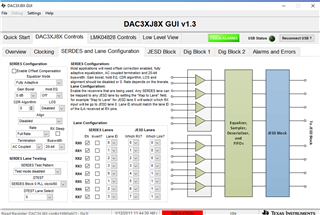

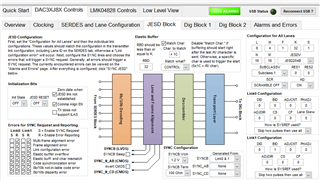

In the DAC3XJ8X GUI we see Link Configuration errors.

Our current FW scheme is the following:

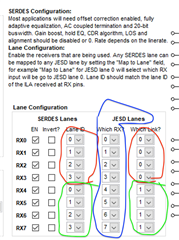

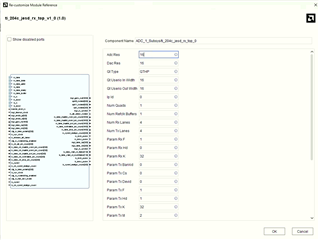

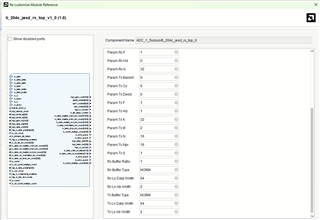

We are using two of the TI JESD204 cores, one for each ADC (4 RX lanes per ADC) and we use 4 TX lanes from each IP core for the full 8 lanes required for our DAC.

Currently, our ADC works well and the GBTs from the FPGA side and the ADC/DAC side are all locking successfully, but we always have "Link Configuration Errors".

Is it possible to run the DAC using two separate TI IP cores? Right now it is set to LMFS=8411, K=32.

Do we need to just be using a single core for the DAC?

Thanks,

Ryan