Tool/software:

Hi team,

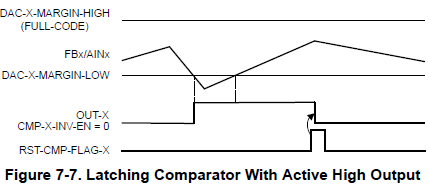

My customer considers using programmable hysteqresis comparator mode and latching comparator with active high output. Please look at the figure 7-7 on the datasheet. In this mode, does OUT-X continues high when FBx/AINx lowers DAC-X-MARGIN-LOW and RST-CMP-FLAG-X gets high? In figure 7-7, OUT-X gets low because FBx/AINx is higher than DAC-X-MARGIN-LOW and RST-CMP-FLAG-X gets high, but what would it happen when FBx/AINx is lower than DAC-X-MARGIN-LOW and RST-CMP-FLAG-X gets high?

Best regards,

Shunsuke Yamamoto