Tool/software:

Hi,

I want to interface the LVDS Differential O/Ps of this ADC to Virtex Ultrascale Plus FPGA with HP IO bank.

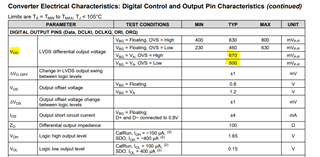

Below is from ADC datasheet.

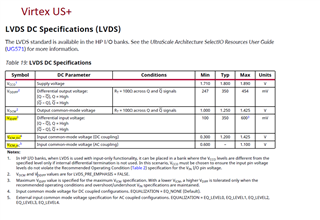

Below is Virtex Ultrascale FPGA HP IO bank characteristics (Link) : table 19

1. What is the Common mode voltage of the differential ADC Outputs for AC and DC coupling? Will it match the FPGA receiver characteristics highlighted above?

2. Based on FPGA datasheet, Differential mode spec of FPGA is max 600mV. Is this an issue to integrate with the ADC outputs?

We have previous used Virtex6 in older design with same ADC and didn't see any issue on this. But since we are going for a new FPGA, want to be sure of this.

Thanks.