Tool/software:

Hello team,

My customer has several questions regarding clock and conversion timing.

Would it be possible to answer questions below?

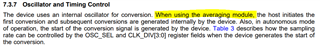

1. When customer is not using averaging filter, can they ignore OSC_SEL and CLK_DIV[3:0] setting? It seems like they are only used for averaging module.

2. What is the benefit or usecase of Manual Mode over On-the-Fly mode? It seems like On the fly mode is better because there is no latency for channel selection.

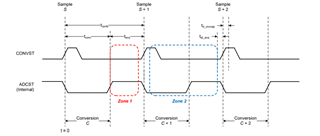

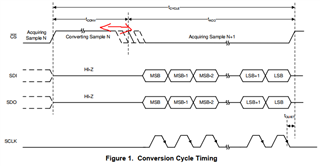

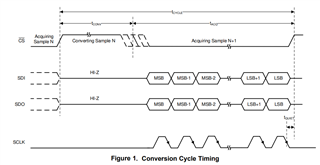

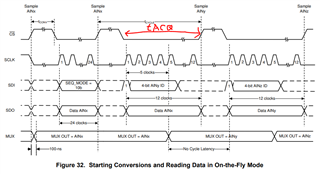

3. What is the Figure 1 (Conversion Cycle Timing) implying?

Does it mean that user has to pull CS HIGH to start conversion and pull CS LOW manually to start sample acquisition?

OR is it going to start the Acquisition automatically, when conversion is done. Will it pull the CS by the ADC?

4. tACQ is 400ns (MIN) from the datasheet.

When 50MHz of SPI is used, the 12 clock would be 240ns, so it seems impossible to achieve 400ns of tACQ.

Is this true?

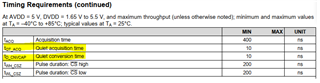

5. What are Quiet acquisition time and quiet conversion time? I couldn't find any explaination from the datasheet.

Best Regards,

Kei Kuwahara