Tool/software:

We have recently started to use the TI DAC8740H HART modem in our product. While performing some basic product testing we noticed that HART communication is not always working. After more detailed investigation we have observed that the DAC8740H HART modem is dead after power cycle.

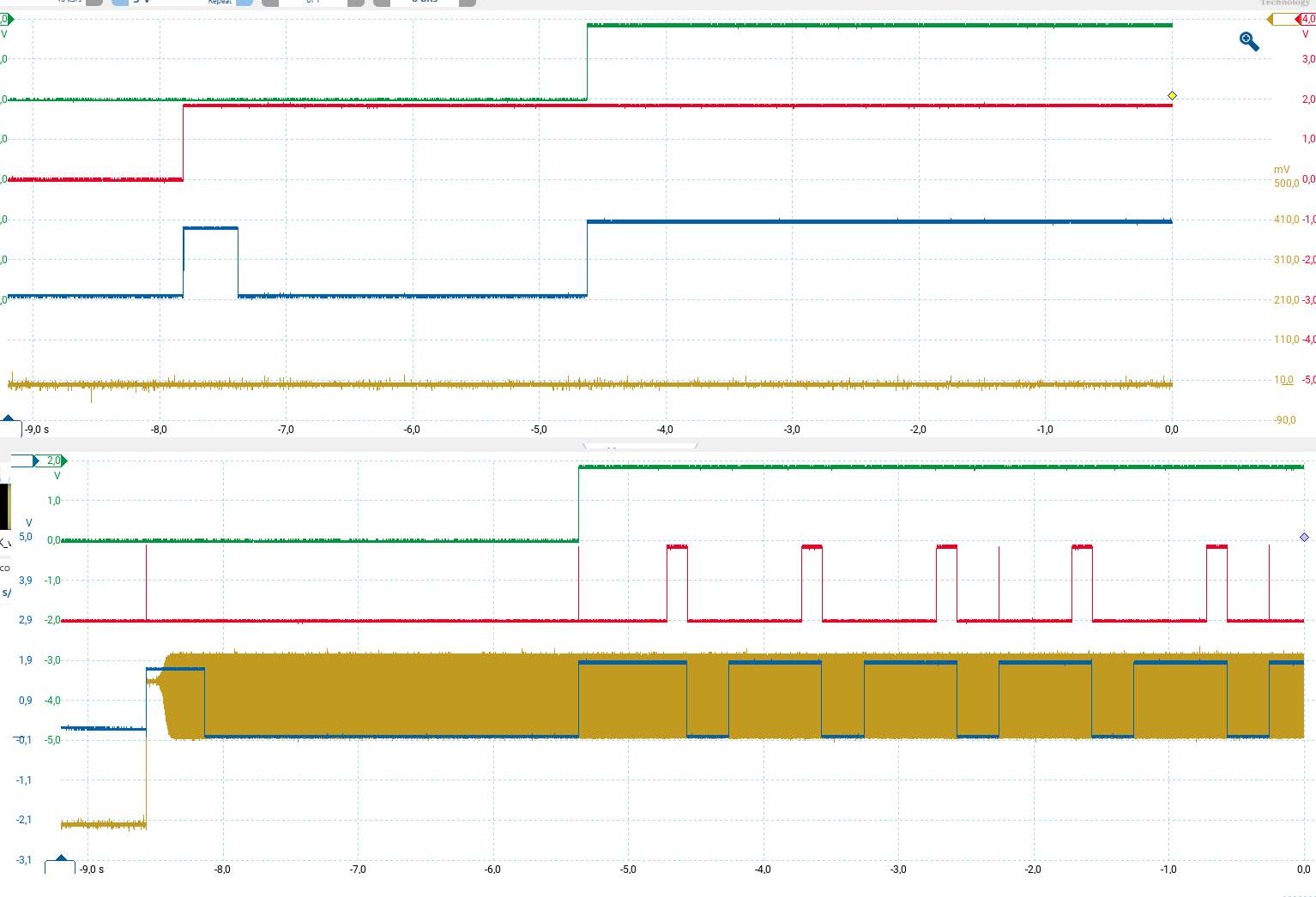

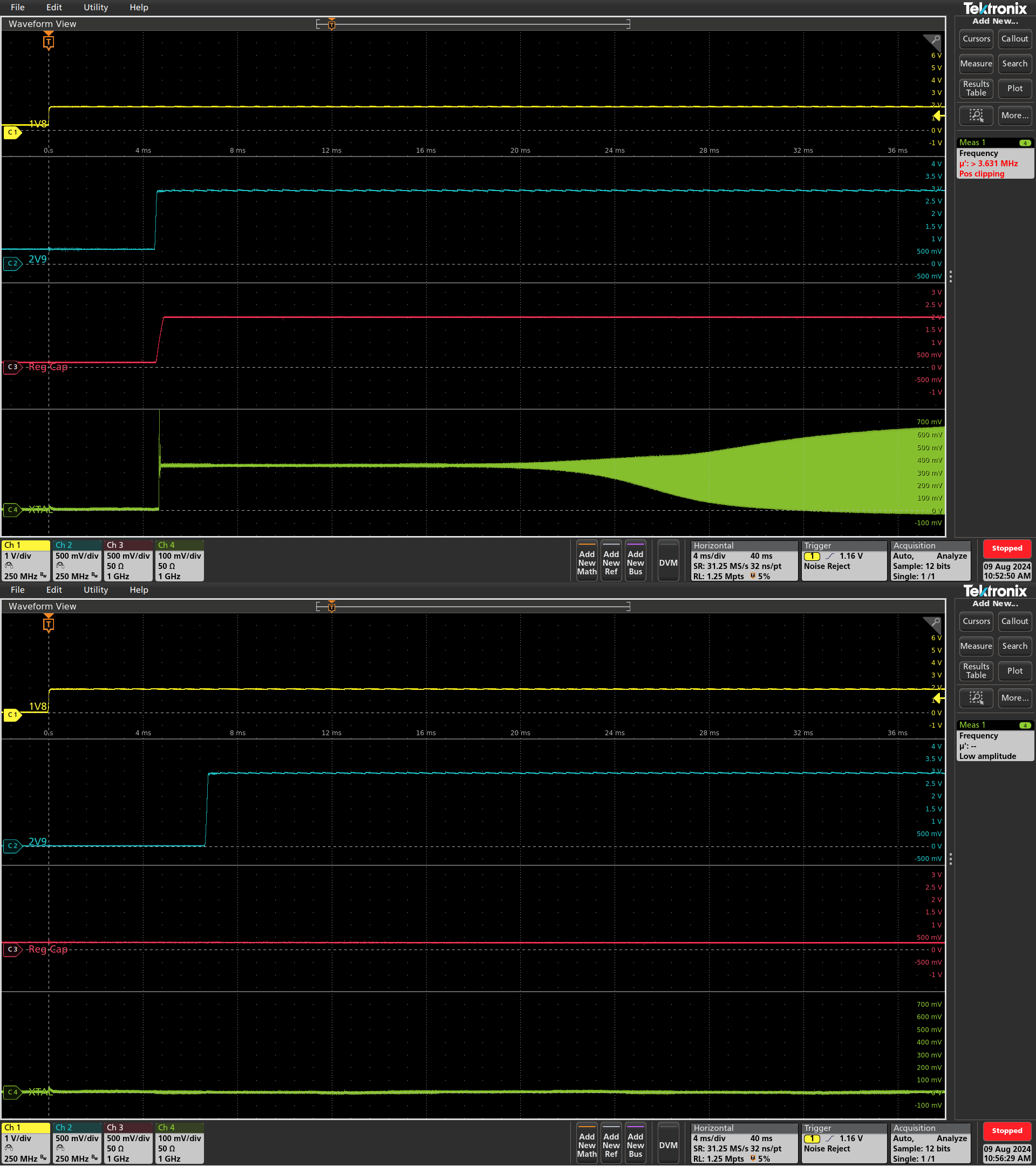

We have external oscillator attached to the DAC8740H and AVDD supply is 2.9 V and IOVDD supply is 1.8 V. In the dead situation the external crystal oscillator is not started and the REG_CAP pin show low voltage. In our design we provide first IOVDD and approximately after 6 ms AVDD is put on. If we reverse the supply voltage order then we are not able to see the dead situation.

From the datasheet I could not find if the order for the AVDD and IOVDD matters? What do you experts think about this problem?