Tool/software:

Recently I ran into some issues while debugging ADS131M08. Some features of ADS131M08 are not well understood.

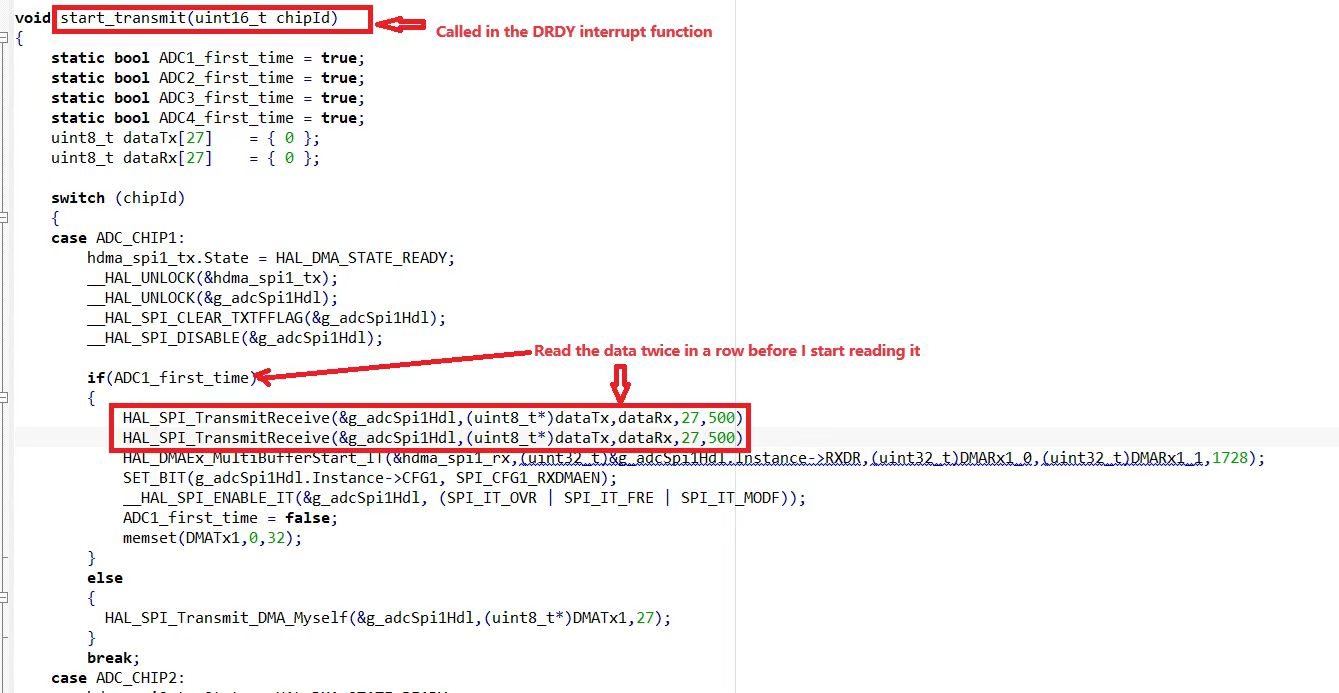

My project is to use STM32H7 as micro control, SPI+DMA way to read data.

Following the instructions in the data sheet, two consecutive frames are read before DMA is enabled. Why read two frames in a row first? I didn't do what the manual said, so DRDY no longer behaves at the rate I set. For example, I set it to 8KSPS, but the actual performance rate is less than 1K.

I actually want to know the detailed mechanism between the behavior of the DRDY pin and the 2 'FIFO inside the device. ”